梳理STM32芯片的内部架构

STM32芯片主要由内核和片上外设组成,STM32F103采用的是Cortex-M3内核,内核由ARM公司设计。

芯片(也称集成电路,IC)是一种将多个电子组件集成在一个小型半导体基板上的电子元件。芯片是现代电子设备的核心部分,负责计算、存储、输入输出等功能。常见的芯片类型包括中央处理器(CPU)、图形处理单元(GPU)、存储芯片等。随着技术的进步,芯片的计算能力和集成度不断提高,推动了智能手机、计算机、物联网设备等电子产品的快速发展。

STM32芯片主要由内核和片上外设组成,STM32F103采用的是Cortex-M3内核,内核由ARM公司设计。

本文将单片机在安全保护方面的发展历程与大家分享。并在文章的最后,总结了现阶段安全级别最高的智能卡芯片的优点及其缺点。

根据MarketWatch发布的报告显示,世界范围内的芯片短缺现象预计还会持续三四个季度,如果准确的话,要到2022年的某个时候,行业才会恢复正常。

晶体管发明并大量生产之后,各式固态半导体组件如二极管、晶体管等大量使用,取代了真空管在电路中的功能与角色。到了20世纪中后期半导体制造技术进步,使得集成电路成为可能。

中美贸易摩擦已经延伸到半导体领域,我们更清楚地认识到大力发展本土集成电路产业的重要性和迫切性......为此,电子创新网推出“毛衣战下的本土精品IC推介会”系列活动,我们欢迎更多本土精品IC报名参加推介活动。

在我们阐明半导体芯片之前,我们先应该了解两点。其一半导体是什么,其二芯片是什么。半导体( semiconductor),指常温下导电性能介于绝缘体(insulator)与导体(conductor)之间的材料。人们通常把导电性差的材料,如煤、人工晶体、琥珀、陶瓷等称为绝缘体。而把导电性比较好的金属如金、银、铜、铁、锡、铝等称为导体。

芯片设计行业是典型的高投入,高收益的行业,但是也是一个风险非常大的行业,万一设计的芯片达不到预期,巨额投入就打了水漂。下面说说一颗芯片的成本构成,以及一枚芯片的售价是如何定义出来的。

芯片的成本包括芯片的硬件成本和芯片的设计成本:

芯片硬件成本

芯片硬件成本包括晶圆成本+掩膜成本+封装成本+测试成本四部分,写成一个公式就是芯片硬件成本=(晶圆成本+掩膜成本+封装成本+测试成本)/最终成品率

晶圆是制造芯片的原材料,晶圆成本可以理解为每一片芯片所用的材料(硅片)的成本。在产量足够大,以亿为单位来计算的话,晶圆成本在硬件成本里面占比是最高的。

掩膜成本就是采用不同的制程工艺所花费的成本,像40/28nm的工艺已经非常成熟,40nm低功耗工艺的掩膜成本为200万美元;28nmSOI工艺为400万美元;28nmHKMG成本为600万美元。但是最先进的制程工艺,那就是天价了。14nm制程工艺在2014年刚投入生产的时候,掩膜成本是3亿美元;而下一代的10nm制程工艺,根据Intel官方估算,掩膜成本至少需要10亿美元。

芯片作为微处理器或多核处理器的核心,它可以控制计算机、手机等产品,是它们的“大脑”。近年来,随着各个国家对芯片产业的重视,纷纷加大对芯片的研究力度,芯片热成为2018年整个产业的一大亮点。

设计开发一个芯片需要很多的技术,随着人们对小尺寸和高集成度的要求,芯片越来越小,功能却越来越多。对于芯片制造工艺和设计,市场有很多新的要求。2018年是“芯”品频出的一年,笔者盘点了这一年非常具有代表性的十大新品,它们来自于全球各大知名企业。(排名不分先后)

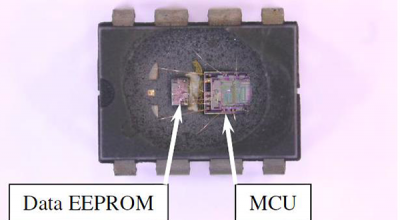

1、上海贝岭EEPROM存储芯片

2018年7月,在由众多业内媒体策划的第一届“我用中国芯”最佳半导体芯片评选中,上海贝岭股份有限公司的2Mbit的EEPROM BL24CM02芯片荣获存储类的最受欢迎芯片奖和最佳芯片奖。据悉,上海贝岭的EEPROM产品,封装形式从SOP、DIP、TSSOP、UDFN、TSOT23到WLCSP都有,产品特点是零静态功耗、品质可靠等,在网通设备、仪表、CCM等领域都可应用。

2、百度AI芯片“昆仑”

在线烧录因集烧录测试一体的优势受到众多用户喜爱,但却往往因连接工装,夹具导致接线过长,进而增加不稳定性和烧录不良率,这究竟要如何改善呢?

1. 增加屏蔽层,防止电磁干扰、静电干扰

元器件选型基本原则:

1)普遍性原则:所选的元器件要是被广泛使用验证过的,尽量少使用冷门、偏门芯片,减少开发风险。

2)高性价比原则:在功能、性能、使用率都相近的情况下,尽量选择价格比较好的元器件,降低成本。

3)采购方便原则:尽量选择容易买到、供货周期短的元器件。