瑞芯微发布24合1视频桥接芯片RK628D

RK628D支持三种输入接口,九种输出接口,仅一颗芯片即可实现多达24种视频传输转换接口的组合。

芯片(也称集成电路,IC)是一种将多个电子组件集成在一个小型半导体基板上的电子元件。芯片是现代电子设备的核心部分,负责计算、存储、输入输出等功能。常见的芯片类型包括中央处理器(CPU)、图形处理单元(GPU)、存储芯片等。随着技术的进步,芯片的计算能力和集成度不断提高,推动了智能手机、计算机、物联网设备等电子产品的快速发展。

RK628D支持三种输入接口,九种输出接口,仅一颗芯片即可实现多达24种视频传输转换接口的组合。

InnoSwitch4-CZ器件集成了一个采用Power Integrations的PowiGaN™技术的可靠耐用的750V初级开关,以及一个新型高频有源箝位反激式控制器。

MCU芯片在很多领域都有着广泛的应用,在此次“芯片荒”浪潮中,MCU是受影响最严重的芯片。

最初出现芯片供应短缺问题的设备主要包括电源管理、显示设备和微控制器等,这些设备在8英寸芯片代工厂的传统节点上制造,其供应量有限。

简单来说,如果把汽车比作手机,智能座舱就相当于手机通过硬件(如摄像头)、软件升级的方式,让手机使用起来更便捷。

纳芯微宣布推出高性价比三通道数字隔离器NIRS31及RS-485接口隔离芯片NIRS485。

作为一名电源研发工程师,自然经常与各种芯片打交道,可能有的工程师对芯片的内部并不是很了解,不少同学在应用新的芯片时直接翻到Datasheet的应用页面,按照推荐设计搭建外围完事。

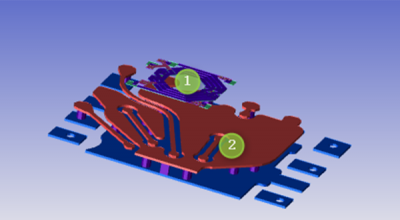

随着5G技术的发展,射频前端(RFFE)设计变得越来越复杂,而系统级封装(SiP)技术因其可集成多颗裸芯片与无源器件的特点,开始被广泛用于射频前端的设计中。

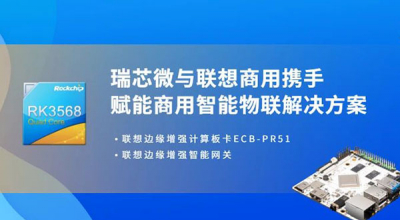

近日,联想商用正式发布了智能物联新产品——基于瑞芯微RK3568芯片研发的联想边缘增强计算板卡ECB-PR51,以及采用此主板开发的联想边缘增强智能网关。

本文件将介绍STM32WB无线产品架构、系列、生态系统及市场应用,帮助您更好了解STM32WB。