纳芯微联合芯弦推出NS800RT系列实时控制MCU

纳芯微今日宣布联合芯弦半导体(ChipSine),推出NS800RT系列实时控制MCU。该系列MCU凭借更加高效、功能更强大的实时控制能力和丰富的外设,使工程师能够在光伏/储能逆变器、不间断电源、工业自动化、协作机器人、新能源汽车大/小三电、空调压缩机等系统中,实现皮秒(万亿分之一秒)级别的PWM控制,从而显著提升系统运行精度和效率。

MCU是Microcontroller Unit(微控制器单元)的缩写,它是一种集成了中央处理器(CPU)、存储器(ROM、RAM)、输入/输出端口(I/O)、定时器(Timer)、串行通信接口(UART、SPI、I2C等)和其他外围设备控制器的单个芯片。MCU通常用于嵌入式系统中,用于控制各种电子设备和系统。

由于其集成度高、体积小、功耗低以及成本相对较低等特点,MCU被广泛应用于各种嵌入式系统中,例如智能家居设备、医疗设备、汽车电子系统、工业自动化等。MCU的选择通常基于应用的需求,如处理性能、功耗、外设接口等因素。

纳芯微今日宣布联合芯弦半导体(ChipSine),推出NS800RT系列实时控制MCU。该系列MCU凭借更加高效、功能更强大的实时控制能力和丰富的外设,使工程师能够在光伏/储能逆变器、不间断电源、工业自动化、协作机器人、新能源汽车大/小三电、空调压缩机等系统中,实现皮秒(万亿分之一秒)级别的PWM控制,从而显著提升系统运行精度和效率。

2024年11月20日,国芯科技的高端动力、底盘、域融合MCU产品CCFC3007、CCFC3008系列成功获得德国莱茵TÜV集团颁发的ISO 26262 ASIL-D功能安全产品认证。

MCU作为编码器设计的核心部件,是系统整体性能的关键所在,极海APM32F103xB磁电式绝对值编码器参考方案,适用于16~21位角度分辨率的应用场景,主要应用于工业控制、消费电子领域,为系统控制提供准确的位置信息。

AT1121+MCU A1是一款高集成度、低成本、设计灵活的套片。该套片无需外加语音芯片,实现了软件集成语音播报功能。提供定制语音库,可灵活选择多种音色播报的语言。

针对G32A14XX系列汽车通用MCU,极海正式推出具备独立知识产权、完全自主开发的 AUTOSAR MCAL软件包和配置工具,这标志着极海已具备完善的、高水准的、独立自主的AUTOSAR软件开发技术和综合服务能力,成为国内为数不多可以开发和提供符合AUTOSAR标准的软硬件的汽车芯片设计企业之一。

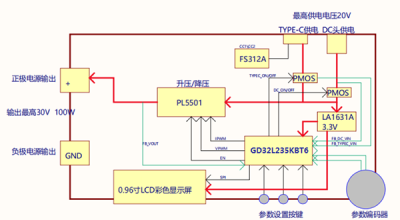

本文介绍基于兆易创新GigaDevice的GD32L235系列MCU设计的微型便携式微型电源方案。

极海携多款产品及MCU+解决方案亮相此次展会(极海展位号:B4.438),全面展示了极海在工业与新能源、电机控制、汽车电子等领域的广泛应用实力。展位自开幕以来,吸引了众多专业观众参观和咨询,现场气氛火热,人潮络绎不绝。

业界领先的半导体器件供应商兆易创新GigaDevice(股票代码 603986)宣布,正式推出基于Arm® Cortex®-M33内核的GD32G5系列高性能微控制器。

本次发布会中,兆易创新展现了其在工业自动化、数字能源等领域的最新成果,不仅重磅揭幕了两款MCU新品——EtherCAT®从站控制芯片和GD32G5系列Cortex®-M33内核的高性能MCU,还同步推出一系列搭载全新MCU产品的电机控制和数字能源方案。

11月11日,“第三届传感器与应用技术大会”在深圳光明云谷国际会议中心盛大召开。本届大会由深圳市光明区人民政府与中国传感器与物联网产业联盟联合主办,旨在响应深圳市“20+8”产业集群发展政策,加速智能传感器技术创新与产业集群发展。