中颖电子获得授权许可将CEVA低功耗蓝牙IP部署用于无线连接MCU

SH87F881X系列无线连接MCU和模块利用CEVA业界领先的低功耗蓝牙 IP来实现超低功耗无线连接

MCU是Microcontroller Unit(微控制器单元)的缩写,它是一种集成了中央处理器(CPU)、存储器(ROM、RAM)、输入/输出端口(I/O)、定时器(Timer)、串行通信接口(UART、SPI、I2C等)和其他外围设备控制器的单个芯片。MCU通常用于嵌入式系统中,用于控制各种电子设备和系统。

由于其集成度高、体积小、功耗低以及成本相对较低等特点,MCU被广泛应用于各种嵌入式系统中,例如智能家居设备、医疗设备、汽车电子系统、工业自动化等。MCU的选择通常基于应用的需求,如处理性能、功耗、外设接口等因素。

SH87F881X系列无线连接MCU和模块利用CEVA业界领先的低功耗蓝牙 IP来实现超低功耗无线连接

我们都知道硬件看门狗的目的:是用来监测系统,防止系统死机,并在死机的情况下使其系统复位重启。

爱普特推出的基于全国产RISC核自研的APT32F110X的充气泵控制方案,自带LCD显示驱动,可节省驱动IC,降低方案成本,提高产品竞争力。

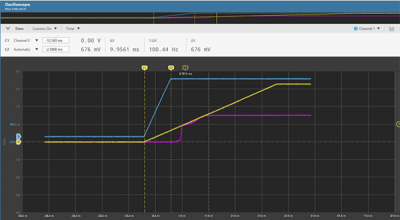

近年来国产厂商积极布局各系列MCU产品线,开始逐渐在特定细分领域实现突破。而最近两年来下游需求强劲,供应端却吃紧,国内设计公司面临着极大的Time to Market的时间压力,高端领域的MCU对质量的诉求也极高。如何高效地进行测试开发,快速定位芯片失效问题并进行质量把控,是MCU芯片厂商急切希望解决的问题。

家用血氧仪的结构和功能都较为简单,主要由一颗MCU控制芯片,配合光电二极管等外围器件电路组成,实现信号采集、数据分析和结果显示等功能。其中带有低功耗、高精度ADC等功能的MCU芯片是保证血氧仪精确度的核心器件。

PEmicro宣布,其开发与烧录工具现已全面支持极海APM32F0、APM32F1、APM32F4系列MCU。通过使用Cyclone Programmers,可安全可靠地烧录上述APM32 系列MCU,为用户提供更好性能。

IAR Systems嵌入式开发解决方案现已全面支持兆易创新GD32系列芯片,与合作伙伴一同提升产业影响力

海速芯32bit MCU TM32F103K7,采用高性能的ARM Cortex-M3内核,最高工作频率为72MHz,可P2P替换ST的STM32F103C8T6,软件改动小,硬件兼容,能满足P2P替换以及降本的应用需求。

新冠疫情已经肆虐3年,随着12月7日国家“新十条”防疫政策的发布,动态清零时代已成过去, 在各地防疫全面放开的情况下,各地新冠阳性人员激增,尤其出现了一些危重病例,这些危重病例与人体的一个关键指标有关,那就是血氧饱和度!

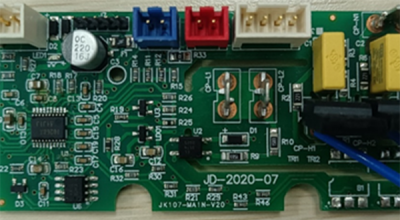

目前已基于RL78 MCU推出多款智能马桶控制主板和模块组件。瑞萨RL78 MCU产品线丰富多样,支持5V供电,外设配置灵活,便于产品持续升级迭代,高可靠性。