相关阅读:

8. 寄存器写保护

寄存器写保护功能可防止重要寄存器因软件错误而被覆盖。使用保护寄存器(PRCR)设置要保护的寄存器。表9列出了PRCR位与要保护的寄存器之间的关联。

图18. PRCR寄存器

表9. PRCR保护位

注:以上寄存器并非存在于所有的RA2产品。具体请参照各MCU硬件手册中“寄存器写操作”的章节。

Renesas FSP提供两个API(R_BSP_RegisterProtectEnable 和 R_BSP_RegisterProtectDisable),分别用于使能和禁用寄存器写保护。

9. I/O 端口配置(1)

《硬件手册》中的“I/O 端口”部分介绍了基于外设选择和其他寄存器设置的确切引脚配置。下面列出了一些一般信息。

务必注意的是,复位后,在应用配置之前,每个引脚都将处于其默认状态。就RA2产品而言,所有I/O引脚在复位后均为输入引脚。其中某些引脚可能会短暂地处于无法预期的状态。无论使用哪种配置方法,都会出现这种情况。用户应考虑这可能对每种应用产生的影响,包括这可能对其他系统功能造成哪些影响。

配置I/O端口时,可以直接写入寄存器,也可以通过FSP引脚配置功能进行配置。

9.1 多功能引脚选择设计策略

RA2系列MCU上的大多数端口都具有多种外设功能。Renesas提供了诸如FSP中的引脚配置器之类的工具,以帮助选择各RA2产品的端口。当需要多个外设功能时,请使用以下设计策略来帮助选择端口功能。

• 首先,仅通过一个端口选项分配外设功能。例如,调试功能中的每个跟踪数据信号只有一个端口选项。需要此功能时,先分配这些端口。

• 接下来,为外设功能分配有限的端口选项。例如,支持CLKOUT外设的产品的每个CLKOUT信号通常只有两个选项。

• 最后,为外设功能分配多个端口选项。一个示例是串行通信接口(SCI),该接口通常具有许多可用的端口选项。

• 从RA2系列MCU硬件手册“引脚列表”章节中可以看到一些端口的函数名称中带有后缀“_A”。为RA2

产品配置端口函数时,可以忽略此种类型的后缀。另请参见本系列文章后续的16.3节。

9.2 设置端口并将其用作GPIO

有两种方法可以设置端口并将其用作GPIO:一种是使用端口控制寄存器(PCNTR1),另一种是使用PmnPFS寄存器。

方法1:端口控制寄存器(PCNTR1)

• 通过向端口控制寄存器1(PCNTR1)的端口方向位 (PDRn) 写入“1”,选择一个引脚作为输出。

• 端口方向位 (PDRn) 是可读写的。将该值设置为“1”将选择该引脚作为输出。I/O端口的默认状态为“0”(输入)。可以在RA2 MCU上读取端口方向寄存器。

• 相应端口控制寄存器 (PCNTR1) 中的端口输出数据位 (PODRn) 是可读写的。读取PODR时,也会读取输出数据锁存器的状态(不是引脚电平)。

• 端口控制寄存器 2 (PCNTR2) 中的端口输入位 (PIDRn) 是只读的。读取PCNTR2寄存器中的 PIDRn 位以读取引脚状态。

方法2:端口mn引脚功能 选择 (PmnPFS) 寄存器

• 端口模式寄存器 (PMR) 是可读写的,用于指定各个引脚是用作GPIO还是用作外设引脚。复位后,所有PMR寄存器均置0,这会将所有引脚都设置为GPIO。如果PMR寄存器置1,则该对应的引脚将用于实现外设功能。外设功能由该引脚的MPC设置定义。

• 将引脚设置为输出时,建议先将所需的端口输出值写入数据锁存器,然后将方向寄存器设置为输出。尽管在所有系统中此操作都不太重要,但这可以防止在设置端口时出现意外的输出毛刺。

通常,使用PCNTR1配置端口有助于提高访问速度,但可用的配置功能较少。使用PmnPFS寄存器将获得更多可用的配置功能,但访问速度较慢。

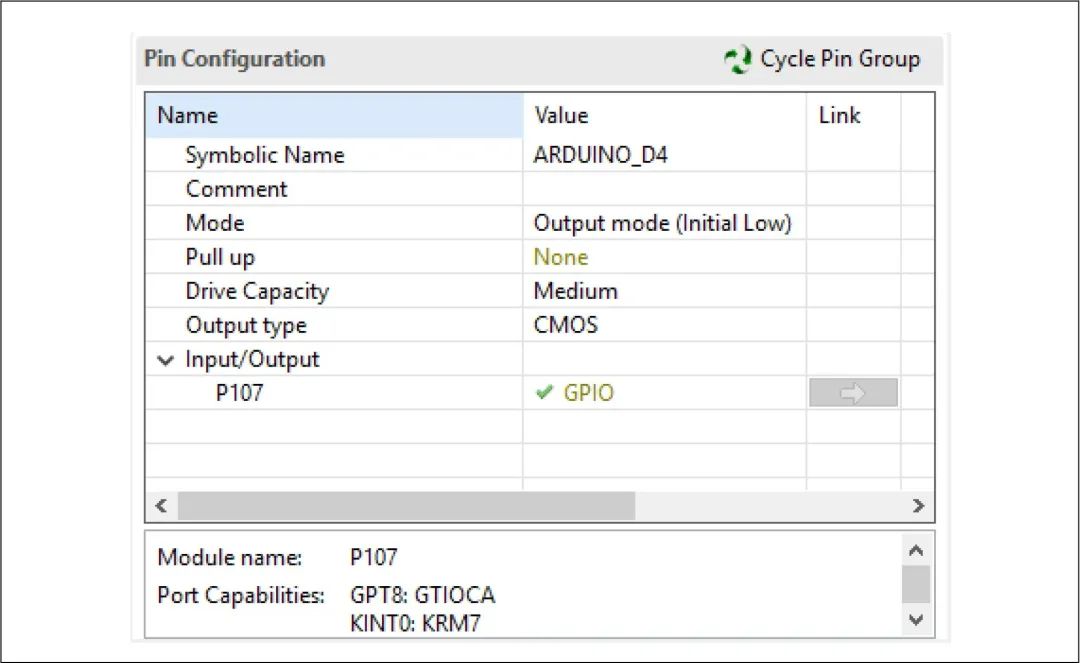

Renesas FSP提供了引脚配置工具,以在复位后配置GPIO引脚,如图19所示。配置GPIO后,可以在FSP中使用HAL层API对该GPIO进行控制

图19. 使用FSP配置器将P107配置为输出和低电平

9.2.1 内部上拉

• 端口0到9上的大多数引脚都可以选择使能上拉电阻。上拉由每个端口mn引脚功能选择 (PmnPFS) 寄存器中的上拉 (PCR) 位控制。每个PmnPFS寄存器中的PCR位用于控制端口上的相应引脚。

• 首先,必须通过PmnPFS寄存器中的相关位将该引脚设置为输入。将PCR位置“1”以使能上拉,将其置“0”以禁用上拉。

• 复位后,会将所有PCR寄存器清零,因此将禁用所有上拉电阻。

• 每当将某个引脚指定为外部总线引脚、GPIO输出或外设功能输出引脚时,上拉就会自动关闭。

9.2.2 漏极开路输出

• 配置为输出的引脚通常用作CMOS输出。

• 端口0到上的大多数引脚都可以选择配置为NMOS漏极开路输出。

• 每个端口9mn引脚功能选择 (PmnPFS) 寄存器中的N沟道漏极开路控制 (NCODR) 位控制哪些引脚以漏极开路模式工作。将每个寄存器中的适用位置“1”会使输出形式变为漏极开路。将每个寄存器中的适用位置“0”会将端口设置为CMOS输出。

9.2.3 驱动能力

RA2A1产品可以使能驱动能力输出,其驱动能力可设为低或中驱动能力输出。其他RA2产品无此功能。

• 驱动能力的切换由每个端口mn引脚功能选择 (PmnPFS) 寄存器中的驱动能力控制寄存器 (DSCR) 位控制。

• 复位后,会将所有DSCR寄存器清零,因此会将所有引脚设置为低驱动能力输出。设置“00”以外的值会更改所选引脚的输出的驱动能力。

• 引脚的最大总输出因产品及封装而异。具体请参见MCU硬件手册“电气特性”章节的内容。

• 驱动能力的差异如下所示。实际输出电流会因产品和引脚类型而有所不同。详细信息请参见MCU硬件手册。

表10. 引脚驱动能力

输出驱动能力可能会对电路板设计的整体性能造成重大影响。为每个输出选择驱动能力时,应考虑以下几点:

• 建议首先将所有引脚设置为低驱动能力(默认)并评估性能。

• 根据电路板布局的不同,驱动能力设置为中或高的引脚可能会产生较高的EMI辐射。

• 较长的走线可能需要更高的驱动能力,才能使信号正确传播到接收器。

9.3 设置和使用端口外设功能

端口mn引脚功能选择寄存器 (PmnPFS) 用于配置每个端口的特性。PSEL 位用于选择为每个端口选择的外设功能。

• 由于大多数引脚具有多种功能,因此RA2 MCU提供了引脚功能控制寄存器 (PmnPFS),可用于更改分配给引脚的功能。

• 每个引脚都有自己的PmnPFS寄存器。

• 每个PmnPFS寄存器都允许将引脚用于外设功能(PSEL位)、用作IRQ输入引脚(ISEL位)或用作模拟输入引脚(ASE位)。如果ASEL位置“1”(将引脚用作模拟输入引脚),则应将该引脚的PMR位置1以用于GPIO,并将该引脚的PDR位置1以用于输入。

• 请参见《硬件手册》中“I/O端口”一章的“每种产品的外设选择设置”部分。

• 为了确保外设引脚上没有非预期的边沿输入或输出,确保在修改引脚的PmnPFS寄存器之前将目标引脚的端口模式控制 (PMR) 位清零。

• 复位后,所有PmnPFS寄存器均受到写保护。为了对这些寄存器执行写入操作,必须首先使用写保护寄存器 (PWPR) 来使能写入。

• 设置PmnPFS寄存器时应格外小心,切勿将一个功能分配给多个引脚。用户不应这样做,但MCU允许上述操作。如果发生这种情况,则引脚上的功能将处于未定义状态。

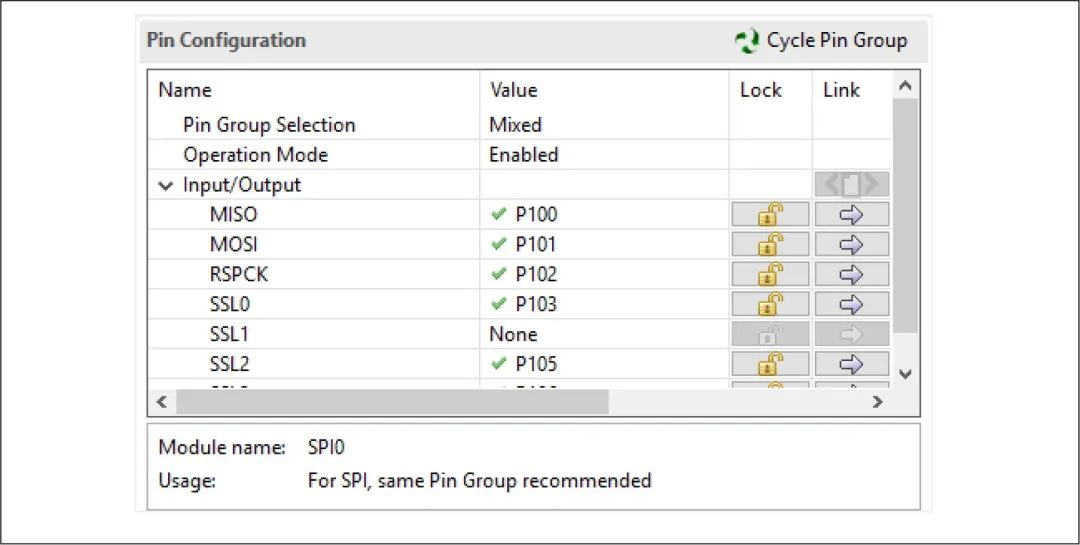

• 图20为使用Renesas FSP的引脚配置器使能QSPI引脚的示例。

图20. 使用Renesas FSP中的引脚配置器使能QSPI引脚

9.4 设置和使用IRQ引脚

• 某些端口引脚可以用作硬件中断线(IRQ)。有关哪些引脚可用于您的MCU的信息,请参见《硬件手册》中“I/O端口”一章的“每种产品的外设选择设置”部分。

• 要将端口引脚设置为用作IRQ引脚,必须将其PFS寄存器中的中断输入功能选择位(ISEL)置“1”。

• 引脚可同时用于IRQ和外设功能。要使能此功能,需设置引脚的PFS寄存器的ISEL位和PSE位。

• 具有相同编号的IRQ功能必须在一个引脚上使能。

• IRQ引脚可以在检测到以下情况时触发中断:

⎯ 低电平

⎯ 下降沿

⎯ 上升沿

⎯ 上升沿和下降沿

使用IRQ控制寄存器(IRQCRi)选择要使用的触发器。

• 数字滤波可用于IRQ引脚。滤波器基于以四个可选时钟速率(PCLKB、PCLKB/8、PCLKB/32、PCLKB/64)之一进行的重复信号采样。它们可以滤除短脉冲:在特定滤波速率下,任何少于3个样本的高脉冲或低脉冲。滤波器可用于滤除这些线路中的振铃和噪声,但是由于速率过快而无法滤除诸如机械开关弹跳之类的长时间事件。使能滤波会给硬件IRQ线增加一小段响应延迟时间(滤波时间)。

• 可以针对每个IRQ引脚单独使能数字滤波。此过程通过设置每个IRQ的IRQCRi寄存器中的IRQ引脚数字滤波器使能(FLTEN)位来实现。

• 可为每个IRQ引脚单独配置数字滤波的时钟速率。此过程通过设置每个IRQ的IRQCRi寄存器中的IRQ引脚数字滤波器设置(FCLKSEL[1:0])位来实现。

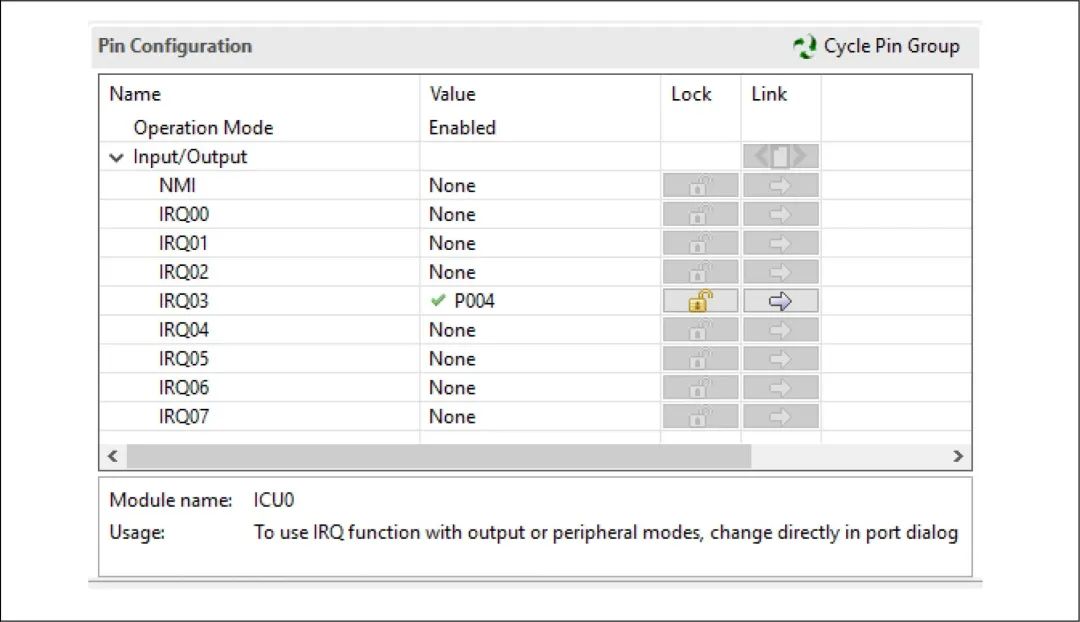

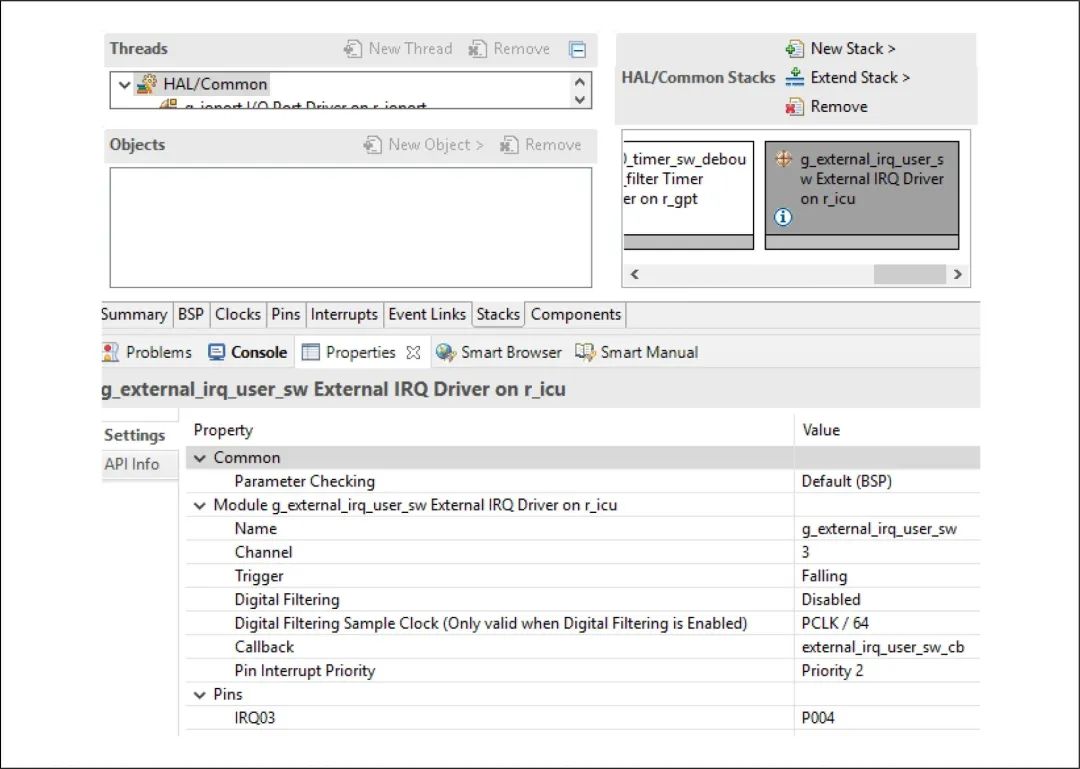

• 图21和图22给出了使用Renesas FSP使能和配置IRQ引脚的示例。

图21. 使用Renesas FSP配置器将P004配置为IRQ03

图22. 使用Renesas FSP配置器配置IRQ03

9.5 未使用引脚的处理

注:某些引脚需要特定的端接:有关具体建议,请参见《硬件手册》中的“未使用引脚的处理”部分。

悬空的未使用引脚会消耗额外的功率,并使系统更容易受到噪声问题的影响。使用下面详述的方法之一对未使用的引脚进行处理:

1、第一种选择是将引脚设置为输入(复位后的默认状态),然后使用电阻将其连接至Vcc或Vss。不同的连接方法对MCU来说没有区别;但是,从系统噪声的角度来看,有的方法可能更具优势。Vss可能是最典型的选择。避免将引脚直接连接到Vcc或Vss,因为对端口的方向寄存器(用于将端口设置为输出)执行意外的写入操作可能会导致输出短路。

2、第二种方法是将引脚设置为输出。无论是将引脚电平设置为高还是低都无关紧要;但是,将引脚设置为输出并将输出设置为低电平会在内部将引脚连接至接地层。这可能有助于解决整个系统的噪声问题。将未使用的引脚设置为输出有一个缺点,即必须通过软件控制来完成端口配置。在将方向寄存器设置为输出前MCU一直保持在复位状态时,该引脚将为悬空输入,可能会消耗额外的电流。如果可以接受在此期间消耗额外的电流,则该方法可消除第一种方法所需的外部电阻。

3、将引脚保留为输入并使用外部电阻将它们处理的一种变化方式是使用MCU多个端口上的内部上拉电阻。这与将引脚设置为输出有相同的限制(需要程序来设置端口),但是由于产品不会驱动引脚,因此确实可以减少因引脚意外接地、短接到相邻引脚或Vcc而产生的影响。

9.6 不存在的引脚

每个RA2 MCU系列都有多种封装尺寸,总引脚数也各有不同。对于小于该MCU系列最大封装尺寸(通常为100引脚、64引脚、24引脚)的任何封装,需将PDR寄存器中不存在的端口的对应位置“1”(输出),并将PODR寄存器中不存在的端口的对应位置“0”。通过查看《硬件手册》中“I/O端口”部分的“I/O端口规范”表,用户可以查看每个MCU封装上可用的端口。例如,端口0上的P007和P008仅在100引脚封装中可用。请注意,不需要对不存在的引脚进行额外处理。

9.7 电气特性

常规GPIO端口通常需要CMOS电平输入(高电平≥ 0.8 * Vcc,低电平≤ 0.2 * Vcc)。某些GPIO端口具有施密特触发输入,在输入要求方面略有不同。有关更多信息,请参见《硬件手册》中的“电气特性”部分。

来源:瑞萨MCU小百科

https://mp.weixin.qq.com/s/FMxRvDbDi1R43nu9Hn8Nsg

https://mp.weixin.qq.com/s/Xknl8CQ0lbxm642YSRcpyA

https://mp.weixin.qq.com/s/oL7o1DdWw4QJat3hjPo4uA

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。