相关阅读:

7. 存储器

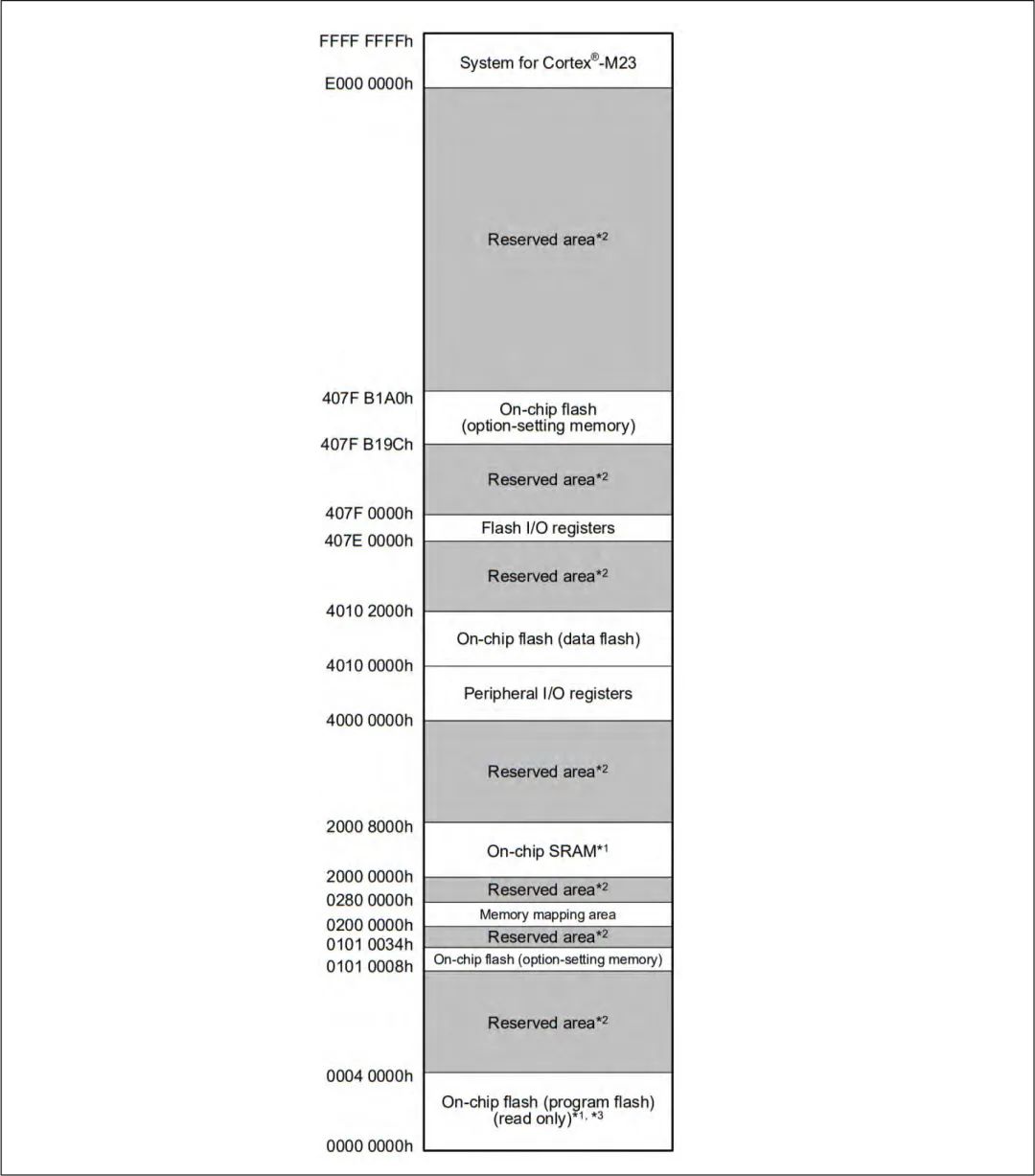

RA2 MCU支持4GB的线性地址空间,范围为0000 0000h到FFFF FFFFh,其中可以包含程序、数据和外部存储器总线。程序和数据存储器共用地址空间;可使用单独的总线分别访问这两个存储器,从而提高性能并允许在同一个周期访问程序和数据。存储器映射中包含片上RAM、外设I/O寄存器、程序ROM、数据闪存和外部存储器区域。

图13. RA2A1存储器映射

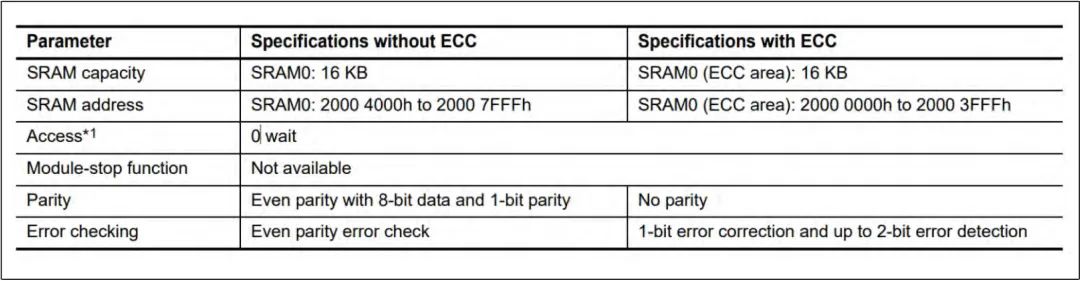

7.1 SRAM

RA2 MCU提供带奇偶校验位或ECC(纠错码)的片上高速SRAM模块。SRAM0的前32 KB区域受ECC控制。奇偶校验在其他区域执行。下表列出了SRAM规范。SRAM模块的数量和容量因产品而异。有关详细信息,请参见《硬件手册》。

图14. RA2A1 SRAM规格

7.2 外设I/O寄存器

外设I/O寄存器块出现在存储器映射中的不同位置,具体取决于设备和当前的工作模式。大多数外设I/O寄存器占用的地址范围为4000 0000h到400F FFFFh。但是,位置和大小可能会因产品而异。有关详细信息,请参见《硬件手册》。有关详细信息,可参见“I/O寄存器”附录,也可参见每个外设功能的寄存器说明。该区域包含在所有工作模式下始终可用的寄存器。用于控制访问闪存的闪存I/O寄存器占据两个区域,即4000 0000h至400F FFFFh和407E 0000h至407E FFFFh。

Renesas FSP包含采用CMSIS数据结构的C头文件,这些文件将特定器件的所有外设I/O寄存器映射到易于访问的I/O数据结构。

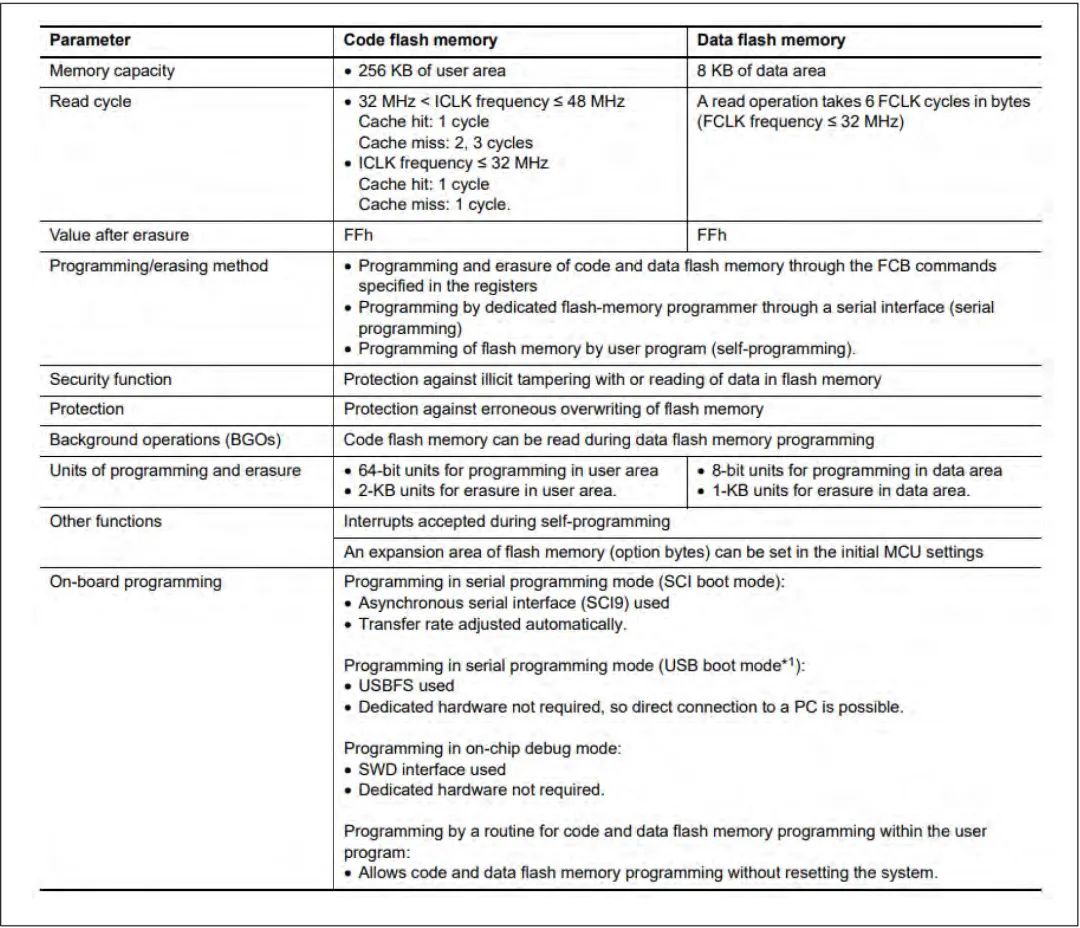

7.3 片上闪存

RA2 MCU具有两个闪存部分:代码闪存和数据闪存,各部分的大小和可编程周期容量因产品而异。闪存控制单元(FCU)控制闪存的编程和擦除。闪存应用程序命令接口(FACI)根据指定的FACI命令控制FCU。

代码闪存旨在存储用户应用程序代码和常量数据。数据闪存旨在存储可能不时更新的信息,例如配置参数、用户设置或记录的数据。数据闪存区域中的编程和擦除单位远小于代码闪存的单位。以RA2A1为例,代码闪存以64-bit为单位进行编程,以2-KB为单位进行擦除;而数据闪存以8-bit为单位进行编程,以1-KB为单位进行擦除。单位大小因产品而已。具体请参见《硬件手册》中的“数据闪存”的章节。

数据闪存和代码闪存区域均可通过应用程序代码进行编程或擦除。这样,无需连接外部编程工具即可完成现场固件更新。

Renesas FSP为代码闪存和数据闪存提供了HAL层驱动程序。

下图给出了代码闪存和数据闪存的规格。

图15. RA2A1 MCU上的代码闪存和数据闪存规范

注:代码闪存的擦除状态为FFh,但数据闪存的擦除状态未定义。

7.3.1 后台操作

RA2 MCU支持通过后台操作访问代码闪存和数据闪存。这意味着当开始执行编程或擦除操作时,用户可以继续从除正在操作的存储区以外的存储区中执行和访问存储器。例如,在对数据闪存进行擦除或编程操作时,CPU可以从代码闪存执行应用程序代码。同样,在对代码闪存进行擦除或编程操作时,CPU可以从SRAM执行应用程序代码。这项规则的唯一例外是,在对代码闪存进行编程或擦除期间无法访问数据闪存。

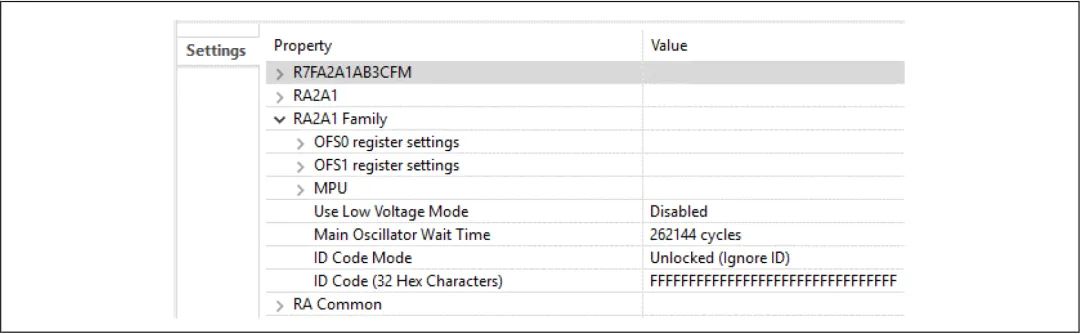

7.3.2 ID代码保护

RA2 MCU在选项设置存储区中有一个用作ID代码的128位存储器。如果此ID代码保留为空(0xFF),则不会使能任何保护,并且可以通过引导模式或使用片上调试器来访问MCU。如果设置了ID代码,则用户可以控制对这些模式的访问。用户可以选择始终禁止连接,或者可以选择在输入匹配的ID代码时允许连接。有关更多信息,请参见“OCD/串行编程ID设置寄存器(OSIS)”和“ID代码保护”以及《RA2 MCU硬件手册》中的相关部分。

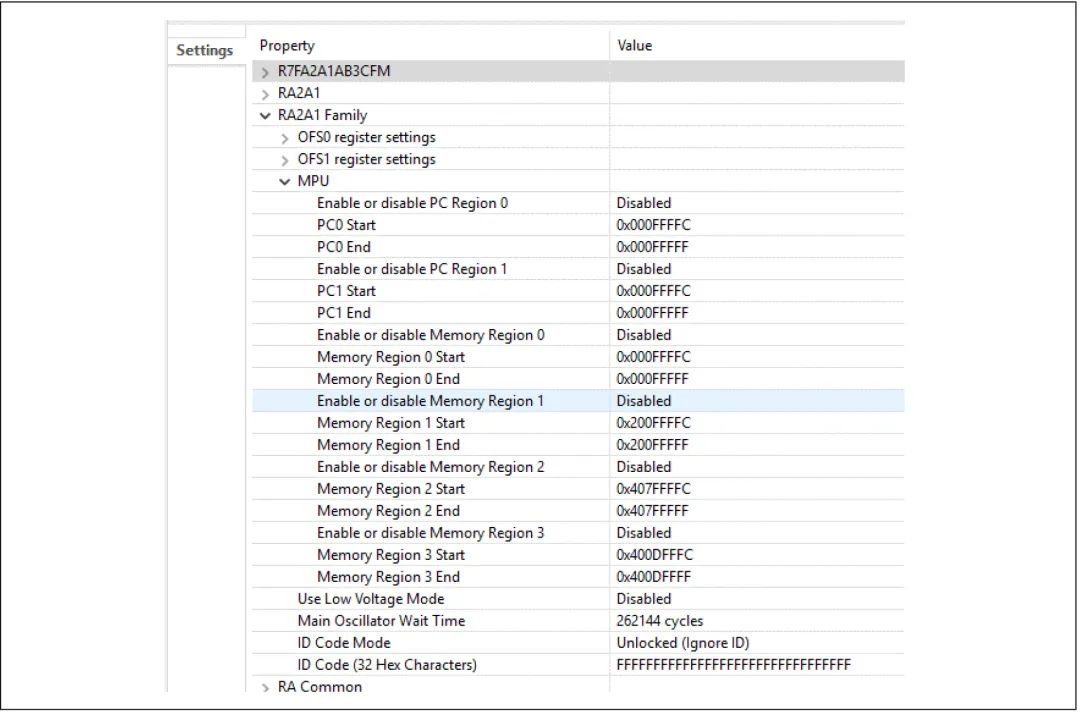

图16 显示了Renesas FSP配置器提供的用于设置ID代码保护的选项。

图16. 使用Renesas FSP配置器为RA2A1设置ID代码

注:必须谨慎处理ID代码保护设置,以避免发生可能导致阻止访问MCU的错误。

7.3.3 存储器保护单元

RA2微控制器具有存储器保护单元(MPU)。这些单元能够保护各种MCU区域免遭非法访问。具体选项包括允许读写、禁止写入和禁止读写。通过在特定的存储器地址上设置相应的常数值可选择这些选项之一。有关更多详细信息,请参见《硬件手册》中的“存储器保护单元”部分。

图17. 使用Renesas FSP配置器RA2A1设置MPU

注:必须谨慎处理MPU设置,以避免发生可能导致阻止访问MCU区域的错误。

7.4 字节顺序的限制

存储器空间必须采用小端法才能在Cortex-M内核上执行代码。

来源:瑞萨MCU小百科

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。