嵌入式单片机程序架构之顺序结构

时间片轮询法,在很多书籍中有提到,而且有很多时候都是与操作系统一起出现,也就是说很多时候是操作系统中使用了这一方法。不过我们这里要说的这个时间片轮询法并不是挂在操作系统下,而是在前后台程序中使用此法。也是本文要详细说明和介绍的方法。

时间片轮询法,在很多书籍中有提到,而且有很多时候都是与操作系统一起出现,也就是说很多时候是操作系统中使用了这一方法。不过我们这里要说的这个时间片轮询法并不是挂在操作系统下,而是在前后台程序中使用此法。也是本文要详细说明和介绍的方法。

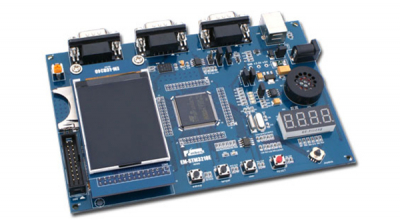

ARM嵌入式系统硬件设计

图1是系统硬件结构图“系统采用外部3.6864MHz的晶振产生内核所需要的18.432MHz、36.864MHz、49.152MHz或73.728MHz的时钟。

做嵌入式系统开发,经常要接触硬件。做嵌入式开发对数字电路和模拟电路要有一定的了解。这样才能深入的研究下去。

下面我们简单的介绍嵌入式开发中的一些硬件相关的概念。

基本功能

单片机的特点:

(1) 受集成度限制,片内存储器容量较小,一般内ROM:8KB以下;

(2) 内RAM:256KB以内。

(3) 可靠性高

(4) 易扩展

(5) 控制功能强

(6) 易于开发

ARM的特点:

本文档提供了5个适用于32位器件和MPLAB® XC32 C编译器的代码示例。读者需要掌

握一些单片机和C编程语言的相关知识。

在uCOS-II实时内核下,对外设的访问接口没有统一完善,有很多工作需要用户自己去完成。串口通信是单片机测控系统的重要组成部分,异步串行口是一个比较简单又很具代表性的中断驱动外设。本文以单片机中的串口为例,介绍uCOS—II下编写中断服务程序以及外设驱动程序的一般思路。

1、uCOS-II的中断处理及51系列单片机中断系统分析

嵌入式Linux系统移植主要由四大部分组成:

• 搭建交叉开发环境;

• bootloader的选择和移植;

• kernel的配置、编译、和移植;

• 根文件系统的制作;

第一部分:搭建交叉开发环境

嵌入式计算不仅需要网络快速、一致的计算,而且也要求系统能够井然有序地将其执行代码和数据,存储在一个“ 共同” 的“ 狭小” 的空间内。

1、鲁棒性法则

嵌入式计算不仅要求系统迅速而有效的计算,而且还要求在某些计算单元出现错误的时候,系统仍然能 够继续正常运行工作。

首先我们来看一下嵌入式WiFi的来源以及与普通WiFi的区别。