嵌入式技术面试时的"10大潜规则"

本文将给大家分享几点找工作过程中存在的“潜规则”内容。

本文将给大家分享几点找工作过程中存在的“潜规则”内容。

嵌入式USB2 (eUSB2) 规格是对USB 2.0规格的补充,前者通过支持USB 2.0接口在1V或1.2V而不是3.3V的I/O电压下工作,解决了接口控制器与高级片上系统 (SoC)工艺节点集成的相关问题。eUSB2 可让SoC体积更小、更节能,从而使工艺节点继续扩展,并提高在智能手机、平板电脑和笔记本电脑等应用中的性能。

类似于电脑程序,手机APP的加载方式,稍微大型的嵌入式系统(Linux),应用程序经过编译、连接之后,形成一个类似于exe、apk的可执行文件,将这个执行文件放置到文件系统中的固定路径下。以Linux为例,常用文件系统ext3、ext4等等

流水线被指令填满时才能发挥最大效能,即每时钟周期完成一条指令的执行(仅指单周期指令)。如果程序发生跳转,流水线会被清空,这将需要几个时钟才能使流水线再次填满。因此,尽量少的使用跳转指令可以提高程序执行效率,解决发案就是尽量使用指令的“条件执行”功能。

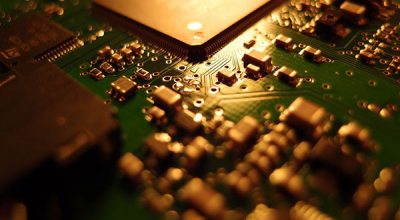

DRAM和SRAM的区别:两者都是随机存取器的一种,上电数据保持,掉电数据消失,不同的是,DRAM需要周期性的更新,SRAM不需要。

在嵌入式软件开发过程中,一般来说,花在测试和花在编码的时间比为3:1(实际上可能更多)。这个比例随着你的编程和测试水平的提高而不断下降,但不论怎样,软件测试对一般人来讲很重要。

什么是嵌入式?什么是单片机?嵌入式和单片机有什么区别和联系呢?本文针对这些问题整理了一篇文章,希望对大家理解单片机和嵌入式的基本概念,以及之间的区别有所帮助。

这十年来我做过小的嵌入式系统,大的电信系统以及基于web的系统。使用过C ++,Ruby,Java和Python等。这篇文章中的经验教训旨在帮助减少编码,测试和调试三个阶段的bug。

工程更改(ECO)将推高设计成本,造成产品开发大量延迟,进而延迟产品上市时间。然而,通过认真思考经常发生问题的七大关键领域,可以规避大多数ECO。这七大领域是:元器件选择,存储器,湿度敏感等级(MSL),可测性设计(DFT),冷却技术,散热器以及热膨胀系数(CTE)。

成为一个正式的嵌入式主板开发工程师,是一个艰辛的过程,需要开发人员维护和管理系统的每个比特和字节。从规范完善的开发周期到严格执行和系统检查,开发高可靠性嵌入式系统的技术有许多种。