PCB表面处理工艺,大全集在这!

PCB表面处理最基本的目的是保证良好的可焊性或电性能。由于自然界的铜在空气中倾向于以氧化物的形式存在,不大可能长期保持为原铜,因此需要对铜进行其他处理。

PCB表面处理最基本的目的是保证良好的可焊性或电性能。由于自然界的铜在空气中倾向于以氧化物的形式存在,不大可能长期保持为原铜,因此需要对铜进行其他处理。

作者:ERIN GOWDY, MENTOR GRAPHICS CORPORATION

就高速ADC PCB的布局布线技巧,之前我们分享过如何实现裸露焊盘的最佳连接。除了需要注意裸露焊盘,小编还要和大家唠唠去耦和层电容~

接地层的使用与上文讨论的星型接地系统相关。为了实施接地层,双面PCB(或多层PCB的一层)的一面由连续铜制造,而且用作地。其理论基础是大量金属具有可能最低的电阻。由于使用大型扁平导体,它也具有可能最低的电感。因而,它提供了最佳导电性能,包括最大程度地降低导电平面之间的杂散接地差异电压。

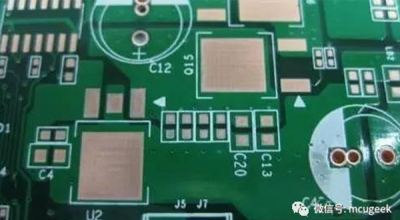

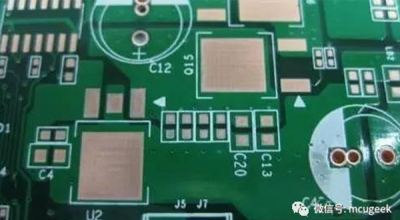

PCB( Printed Circuit Board),中文名称为印制电路板,又称印刷线路板,是重要的电子部件,是电子元器件的支撑体,是电子元器件电气连接的载体。由于它是采用电子印刷术制作的,故被称为“印刷”电路板。

电子设备工作时产生的热量,使设备内部温度迅速上升,若不及时将该热量散发,设备会持续升温,器件就会因过热失效,电子设备的可靠性将下降。因此,对电路板进行散热处理十分重要。

一、印制电路板温升因素分析

引起印制板温升的直接原因是由于电路功耗器件的存在,电子器件均不同程度地存在功耗,发热强度随功耗的大小变化。

本文主要分享差分信号PCB布局布线时的几个常见误区:

很多刚接触阻抗的人都会有这个疑问,为什么常见的板内单端走线都是默认要求按照50欧姆来管控而不是40欧姆或者60欧姆?这是一个看似简单但又不好回答的问题。