PCB板层介绍

PCB板层介绍

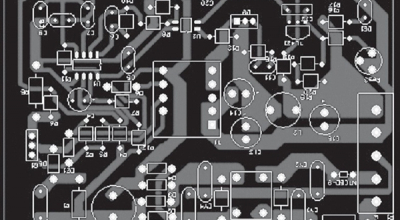

TopLayer(顶层)画出来的线条是红色,就是一般双面板的上面一层,单面板就用不到这层。

BottomLayer(底层)画出来的线条是蓝色,就是单面板上面的线路这层。

MidLayer1(中间层1)这个是第一层中间层,好像有30层,一般设计人员用不到,你先不用管他,多面板时候用的。默认在99SE中不显示,也用不到。

PCB板层介绍

TopLayer(顶层)画出来的线条是红色,就是一般双面板的上面一层,单面板就用不到这层。

BottomLayer(底层)画出来的线条是蓝色,就是单面板上面的线路这层。

MidLayer1(中间层1)这个是第一层中间层,好像有30层,一般设计人员用不到,你先不用管他,多面板时候用的。默认在99SE中不显示,也用不到。

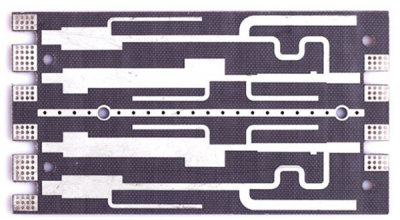

我们预想中的完整 PCB 通常都是规整的矩形形状。虽然大多数设计确实是矩形的,但是很多设计都需要不规则形状的电路板,而这类形状往往不太容易设计。本文介绍了如何设计不规则形状的 PCB。

如今,PCB 的尺寸在不断缩小,而电路板中的功能也越来越多,再加上时钟速度的提高,设计也就变得愈加复杂了。那么,让我们来看看该如何处理形状更为复杂的电路板。

接上一篇:PCB差分走线的阻抗控制技术(一)

方法一:真差分测试法如图6所示:阶跃信号A和阶跃信号B是一对方向相反、幅度相等且同时发出的差分阶跃信号。

一、引言

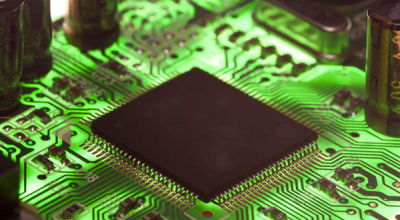

芯片解密主要应用在PCB抄板方面,PCB抄板除了对电路板复制的简单概念,还包括了板上一些加密芯片的解密。随着专利概念和知识保护的加强,芯片解密会慢慢向为程序研究服务方向发展,而不是现在的产品复制方向。

2.1.印制电路板

印制电路板(Printed Circuit Board,简称PCB)在电子设备中是电子元器件的载体,提供机械支撑和电气连接,并保证电子产品的电气、热和机械性能的可靠性。为自动焊锡提供阻焊图形,为电子元器件安装、检查、维修提供识别字符和图形。

1.前言、背景

IPC最新发布的《2016年全球PCB生产报告》显示,2016年全球PCB产值达到582亿美元,实际增长2.2%;北美地区PCB产值下降了0.1%。据《IPC2017年北美地区PCB行业年报》显示,北美市场继续缓慢萎缩,2016年下降了1.7%。

PCB的设计中芯片与PCB互连对设计来说是重要的,然而芯片与PCB互连的最主要问题是互连密度太高会导致PCB材料的基本结构成为限制互连密度增长的因素。本文分享了高频PCB设计的实用技巧。就高频应用而言,PCB板内互连进行高频PCB设计的技巧有:

1、 传输线拐角要采用45°角,以降低回损;

PCB设计是开关电源设计非常重要的一步,对电源的电性能、EMC、可靠性、可生产性都有关联。当前开关电源的功率密度越来越高,对PCB布局、布线的要求也越发严格,合理科学的PCB设计让电源开发事半功倍,以下细节供您参考。

一、布局要求