不规则形状的PCB设计怎么搞?

多数情况下,我们设计以及使用的PCB都是规整的矩形形状,但也有很多时候,我们需要设计出圆形、环形、镂空等不规则形状的电路板,而这类形状的PCB设计往往有些难度。本文将为大家介绍如何设计这些不规则形状的PCB。

多数情况下,我们设计以及使用的PCB都是规整的矩形形状,但也有很多时候,我们需要设计出圆形、环形、镂空等不规则形状的电路板,而这类形状的PCB设计往往有些难度。本文将为大家介绍如何设计这些不规则形状的PCB。

在流程上接收到的资料是否齐全(包括:原理图、*.brd文件、料单、PCB设计说明以及PCB设计或更改要求、标准化要求说明、工艺设计说明文件)。

PCB设计焊点过密,易造成波峰连焊,焊点间漏电。本文为大家来分析下PCB设计焊点过密的优化方式。

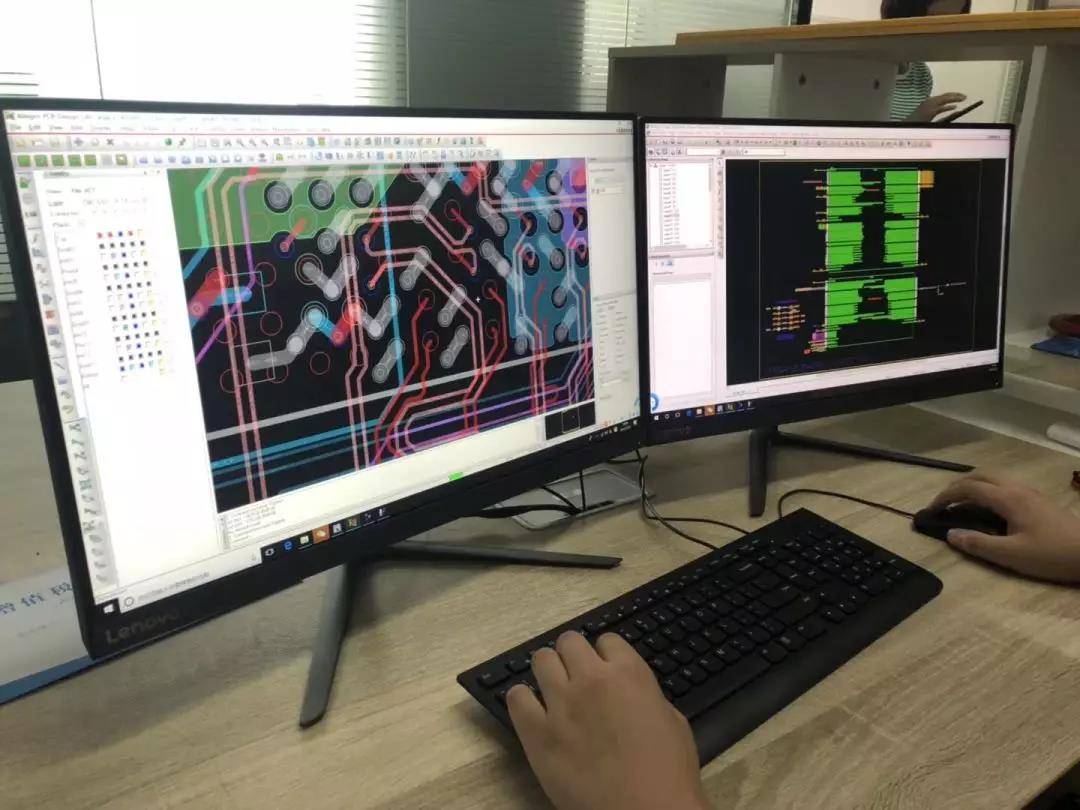

电路板设计是一项关键而又耗时的任务,出现任何问题都需要工程师逐个网络逐个元件地检查整个设计。可以说电路板设计要求的细心程度不亚于芯片设计。

由于体积和尺寸都很小,对日益增长的可穿戴物联网市场来说几乎没有现成的印刷电路板标准。在这些标准面世之前,我们不得不依靠在板级开发中所学的知识和制造经验,并思考如何将它们应用于独特的新兴挑战。

关于PCB设计,是个工程师都有一万句话可以说,无论是经验还是吐槽,或者曾经发生过的PCB设计糗事。当然,我们也会看到各类经验分享的文档,不知大家怎么看PCB设计的规则和经验?

设置安全间距(Clearance Constraint)、设置拐角模式(Rules Corners)、设置PCB设计布线工作层面(Routing Layers)、设置PCB设计布线优先级(Routing Priority)、设置PCB设计布线拓扑结果(Routing Topology)、设置过孔形式(Routing Via Style)、设置PCB设计布线宽度(Width Constraint)

本文就旁路电容、电源、地线设计、电压误差和由PCB布线引起的电磁干扰(EMI)等几个方面,讨论模拟和数字布线的基本相似之处及差别。

在任何开关电源设计中,PCB板的物理设计都是最后一个环节,如果设计方法不当,PCB可能会辐射过多的电磁干扰,造成电源工作不稳定,本文针对各个步骤中所需注意的事项进行分析。

我是一名PCB设计师,接触过的PCB设计产品主要有:射频功放产品、通信直放站产品、航天电子产品、医疗机械电子产品、视频DVD产品、音频MP3产品、安防监控产品等等。因此我从我所站的角度对此话题谈谈我的一些想法,说的不好,请大家多多包涵。

(1) 软件操作