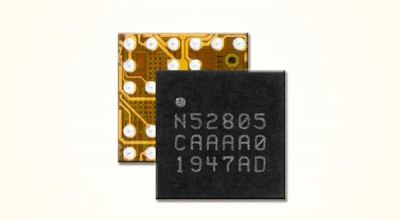

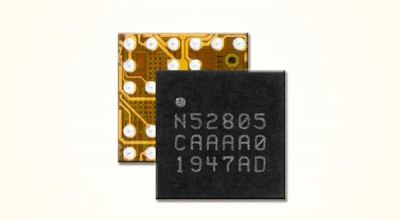

为小型两层PCB设计节省成本:儒卓力提供Nordic 蓝牙5.2 SoC

nRF52805配备了时钟频率为64 MHz的Arm® Cortex®M4处理器。它具有192 KB闪存和24 KB RAM,并集成了多个模拟和数字接口,例如双通道12位 ADC、SPI、UART和TWI。

nRF52805配备了时钟频率为64 MHz的Arm® Cortex®M4处理器。它具有192 KB闪存和24 KB RAM,并集成了多个模拟和数字接口,例如双通道12位 ADC、SPI、UART和TWI。

进行比较复杂的板子设计的时候,必须要进行一些设计权衡。因为这些权衡,那么就存在一些因素会影响到PCB的电源分配网络的设计。

PCB看上去像一个多层蛋糕,制作过程中将不同材料的层,通过粘合剂粘合到一起。从表层开始分别是丝印——阻焊——铜——FR4——铜。。。铜——阻焊——丝印。

焊盘(除表面贴焊盘外)的重叠,意味孔的重叠,在钻孔工序会因为在一处多次钻孔导致断钻头,导致孔的损伤。

随着芯片集成度的增加,PCB板的设计也越来越复杂,PCB的层数也越来越多,在多层PCB中,通常包含有信号层(S)、电源层(PWR)和地层(GND)。

对于电子设备来说,工作时都会产生一定的热量,从而使设备内部温度迅速上升,如果不及时将该热量散发出去,设备就会持续的升温,器件就会因过热而失效,电子设备的可靠性能就会下降。因此,对电路板进行很好的散热处理是非常重要的。

在PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。

在学习PCB设计的过程中,有很多的知识需要大家了解和掌握,比如波峰焊,除了知道什么是波峰焊外,你还需要了解它的PCB设计原则以及布局要求。

在学习PCB设计的过程中,有很多的知识需要大家了解和掌握,比如波峰焊,除了知道什么是波峰焊外,你还需要了解它的PCB设计原则以及布局要求。

焊盘(除表面贴焊盘外)的重叠,意味孔的重叠,在钻孔工序会因为在一处多次钻孔导致断钻头,导致孔的损伤。多层板中两个孔重叠,如一个孔位为隔离盘,另一孔位为连接盘(花焊盘),这样绘出底片后表现为隔离盘,造成的报废。