雅特力AT32F405高速USB MCU荣获“年度最佳MCU”

3月28-29日,由AspenCore主办的2024国际集成电路展览会暨研讨会(IIC Shanghai)在上海张江科学会堂圆满举行。除了众多领域专家的精彩演讲外,2024年中国IC设计Fabless100排行榜也在同期举行的中国IC领袖峰会发布,雅特力AT32F405荣获“中国IC设计成就奖之年度最佳MCU”。

MCU是Microcontroller Unit(微控制器单元)的缩写,它是一种集成了中央处理器(CPU)、存储器(ROM、RAM)、输入/输出端口(I/O)、定时器(Timer)、串行通信接口(UART、SPI、I2C等)和其他外围设备控制器的单个芯片。MCU通常用于嵌入式系统中,用于控制各种电子设备和系统。

由于其集成度高、体积小、功耗低以及成本相对较低等特点,MCU被广泛应用于各种嵌入式系统中,例如智能家居设备、医疗设备、汽车电子系统、工业自动化等。MCU的选择通常基于应用的需求,如处理性能、功耗、外设接口等因素。

3月28-29日,由AspenCore主办的2024国际集成电路展览会暨研讨会(IIC Shanghai)在上海张江科学会堂圆满举行。除了众多领域专家的精彩演讲外,2024年中国IC设计Fabless100排行榜也在同期举行的中国IC领袖峰会发布,雅特力AT32F405荣获“中国IC设计成就奖之年度最佳MCU”。

随着平板电脑在人们日常娱乐、学习、办公中的广泛应用,皮套键盘作为其重要配件,因能够满足快速、大量文字输入的需求,并提供良好的操作体验和PAD保护功能,市场需求呈现稳步增长态势。为此,芯海科技(688595)推出了基于旗下CS32F03X系列MCU产品的平板电脑及其皮套键盘的整体解决方案。

本次研讨会聚焦高性能微控制器HPM6800的产品特性及应用解决方案,吸引了众多企业代表及研发工程师前来参加。

以前微处理器(MPU)与微控制器(MCU)是截然不同的两种设备,MPU支持丰富的软件系统,如Linux和相关的软件堆栈,而MCU通常将专注于裸机和RTOS。近年来,随着MCU的性能越来越高,MCU和MPU之间的区别变得越来越模糊。

近日,全国产32位MCU小巨人企业爱普特微电子宣布推出一款超高性价比的全国产RISC核32位MCU——APT32F1025B,进一步扩展丰富其在全国产、高性价比领域MCU产品系列布局。

全球领先的嵌入式系统开发软件解决方案供应商IAR自豪地宣布:公司备受全球数百万开发者青睐的开发环境再次升级,已率先支持瑞萨首款通用32位RISC-V MCU,该 MCU 搭载了瑞萨自研的 CPU 内核。

智能物联设备的应用场景中,低资源占用和低功耗需求是实现复杂图形用户界面不易跨越的技术难点。MCU作为嵌入式产品的核心,它的图形处理性能日益成为关注焦点。STM32可以为用户提供丰富且具备优异显示效果的多种解决方案。

兆易创新正式推出全新GD32E235系列超值型MCU,进一步扩充Cortex®-M23内核产品阵容。首颗同系列产品Arm® Cortex®-M23内核GD32E230 系列MCU自2018年上市以来,凭借其卓越的性价比优势,在多个市场领域成功替代了Cortex®-M0/M0+产品,并以显著的市场占有率屡获行业殊荣,赢得了广大用户的信赖与支持。

自动换档功能的实现其实是采用拨档开关替代手动操作,拨档开关会根据汽车不同发动机转速、汽车速度以及驾驶员的踩油门的意图来控制拨叉切换和档位切换。

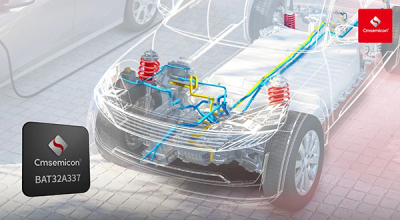

近日,中微半导体(深圳)股份有限公司(以下简称:中微半导 股票代码:688380)宣布推出通过AEC-Q100 Grade 0的32位车规MCU BAT32A337系列。