浅谈STM32在应用中编程(IAP)的应用(俗称在线更新程序)

STM32等单片机是可编程处理器,内部运行着我们编写的程序,而把我们编写的程序“下载”到单片机中,方法有两种:① 使用烧写器,如jlink,stlink,串口下载(需要配置boot0,boot1)。② 通过IAP实现一个在线更新功能。

STM32是STMicroelectronics(意法半导体)推出的一系列基于ARM Cortex-M内核的32位微控制器(MCU)产品。这些微控制器提供了广泛的产品系列,覆盖了多种不同的性能和功能需求,适用于各种应用领域,包括工业控制、汽车电子、消费类电子、医疗设备等。

STM32系列微控制器以其高性能、低功耗、丰富的外设接口和灵活的开发工具而闻名。它们通常具有丰富的存储器、多种通信接口(如UART、SPI、I2C、CAN等)、模拟数字转换器(ADC)、定时器、PWM输出等功能,以满足不同应用场景下的需求。

STM32微控制器通常使用标准的ARM Cortex-M内核,包括Cortex-M0、M0+、M3、M4和M7等,这些内核具有不同的性能和功耗特性,可根据具体应用的需求进行选择。此外,STM32系列还提供了多种封装和引脚配置,以满足不同尺寸和集成度的要求。

STMicroelectronics为STM32系列提供了丰富的开发工具和支持资源,包括基于ARM开发环境的集成开发环境(IDE)、调试器、评估板和参考设计等。这些工具和资源有助于开发人员快速开发和部署他们的应用,并提供了全面的技术支持和文档资料,帮助用户充分发挥STM32微控制器的性能和功能优势。

STM32等单片机是可编程处理器,内部运行着我们编写的程序,而把我们编写的程序“下载”到单片机中,方法有两种:① 使用烧写器,如jlink,stlink,串口下载(需要配置boot0,boot1)。② 通过IAP实现一个在线更新功能。

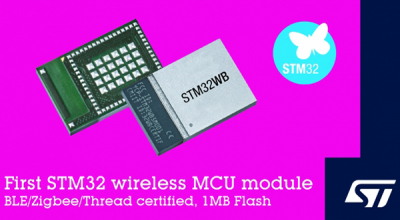

意法半导体推出一个新的加快物联网产品上市的解决方案,该方案可利用现成的微型STM32无线微控制器(MCU)模块加快基于Bluetooth® LE和802.15.4新物联网设备的开发周期。

串口发送数据最直接的方式就是标准调用库函数 。

我们学51单片机就知道,单片机之所以能够单独工作,就是因为他又独立的时钟(晶振),那如果想关闭某些功能,就直接关闭它的时钟就好了,所以就出现了这么多的时钟和IO配置。

不同的平台的汇编代码是不一样的,最早的汇编在50年代就发明了,比很多人的父母的年龄都大,老掉牙,不用学习怎么写汇编。一个公司有一个人知道怎么写汇编就够了。但要学习读汇编,为什么学习汇编?

Multiprotocol LPWAN 32-bit Arm Cortex-M4 MCUs, LoRa, (G)FSK, (G)MSK, BPSK, up to 256KB Flash, 64KB SRAM

Bootloader是硬件启动的引导程序,是运行操作系统的前提。在操作系统内核或用户应用程序运行之前运行的一段小代码。对硬件进行相应的初始化和设定,最终为操作系统准备好环境。

意法半导体与施耐德电气 联合推出一款物联网传感器原型。通过监测建筑物的居住率和使用率,该解决方案可以实现新型物业管理服务,提高楼宇的能源管理效率。

本培训资料包含基于STM32常规定时器由浅入深的基本原理介绍,以及丰富的应用提醒和实际案例分析,图文并茂,值得一看……

意法半导体新推出的STM32 * Nucleo Shield显示板卡开创物联网产品人机界面之先河。新SPI Shield显示板卡X-NUCLEO- GFX01M1利用STM32G0微控制器(MCU)的经济性,支持引入低成本非内存映射SPI闪存IC支持等新功能的最新版TouchGFX软件(4.15.0版)。