你总得知道你为什么要用Cortex-M

来源:周立功单片机

无论您是资深嵌入式工程师,还是怀着满满好奇的嵌入式小白,总会有这样的一些疑惑:Cortx-A、R、M到底什么区别呢?M0、M0+、M3、M4又有什么差异呢?。本文就教您给他们这些亲兄弟算一笔明白账。

来源:周立功单片机

无论您是资深嵌入式工程师,还是怀着满满好奇的嵌入式小白,总会有这样的一些疑惑:Cortx-A、R、M到底什么区别呢?M0、M0+、M3、M4又有什么差异呢?。本文就教您给他们这些亲兄弟算一笔明白账。

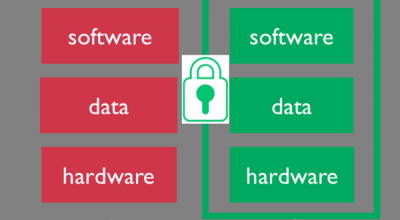

ARM® TrustZone® 是针对片上系统(SoC)设计的系统级安全技术,它基于硬件,内置于CPU和系统内核,为半导体芯片设计师设计设备安全性能(如可信根)量身打造。TrustZone可用于任何基于ARM Cortex®-A的系统,随着全新Cortex-M23和Cortex-M33处理器的发布与升级,Cortex-M也已经支持该技术。

NASA成功发射SpaceX CRS-10货运飞船进行第十次国际空间站商业货运任务。SpaceX CRS-10搭载了一个电子辐射效应实验,关键是该实验由美国Vorago公司的ARM架构抗辐射MCU进行控制。2016年,NASA宣布将选择ARM Cortex-A53处理器构建下一代空间电子产品平台,计划于2020年发射。可见,ARM技术在航天工业中势头越来越猛。

高性能,高能效,易于使用

本文介绍了ATSAMA5 ARM Cortex-A5 MPU和基于ARM9的ATSAM9 MPU的性能参数及适用的评估工具包。

ARM表示OpenSynergy公司正在为其最先进的实时安全处理器ARM® Cortex®-R52 开发业界第一款软件管理程序。该管理程序可将任何基于Cortex-R52的芯片变为虚拟机,并能同时执行不同的软件任务。针对诸如无人驾驶和工业控制系统等设备中芯片不断提升的复杂性,该方法可以将安全性至关重要的功能与无需严格控制的功能相隔离。

来源:赛迪顾问

一、下游应用牵引MCU产业前景向好

(一)物联网

单片机、ARM、DSP这三者都可以说是CPU,那这三者有什么区别吗?

摘要: 作为32位RISC 微处理器主流芯片, ARM 芯片得到长足发展和广泛应用。因而, ARM 芯片的测试需求更加强劲的同时,测试工作量在加大,测试复杂度也在增加.本文给出了基于ARMCo rte x-M3 的微处理器测试方法,该方法也可用于类似结构的微处理器测试。

目前可穿戴设备中无线连接方式以蓝牙最为普遍,这也是因为很多早起的可穿戴设备是手机的附件的原因。当然,蓝牙技术的普及程度,以及模块化也有效促进了可穿戴设备选择蓝牙作为连网手段。对此,ARM的专家为您分析了Cortex-M系列微控制器对于蓝牙连网和可穿戴产品设计中的重要作用。

要了解arm中断系统,GIC绝对不容错过,好先付上一张大家都能百度到的图片。