上一章节对CKS32F107xx系列时钟做了整体介绍,本章节以使用HSI内部高速时钟为例对时钟具体配置方法进行讲解。

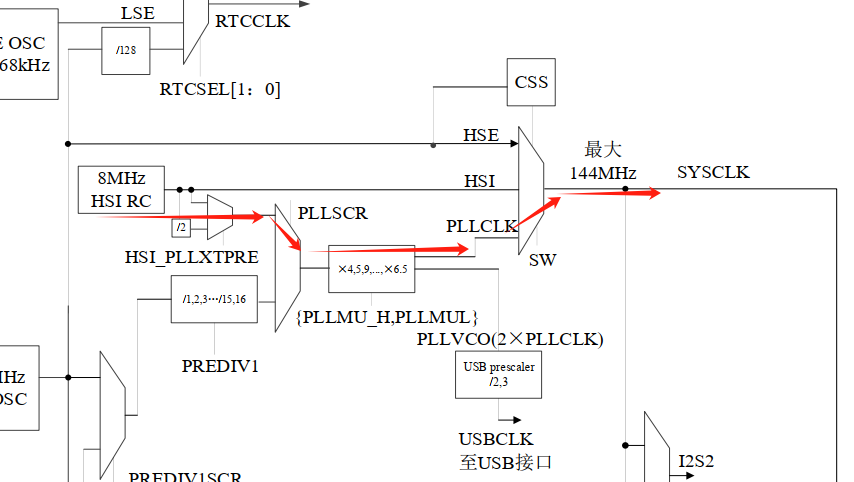

图1 SYSCLK生成流程

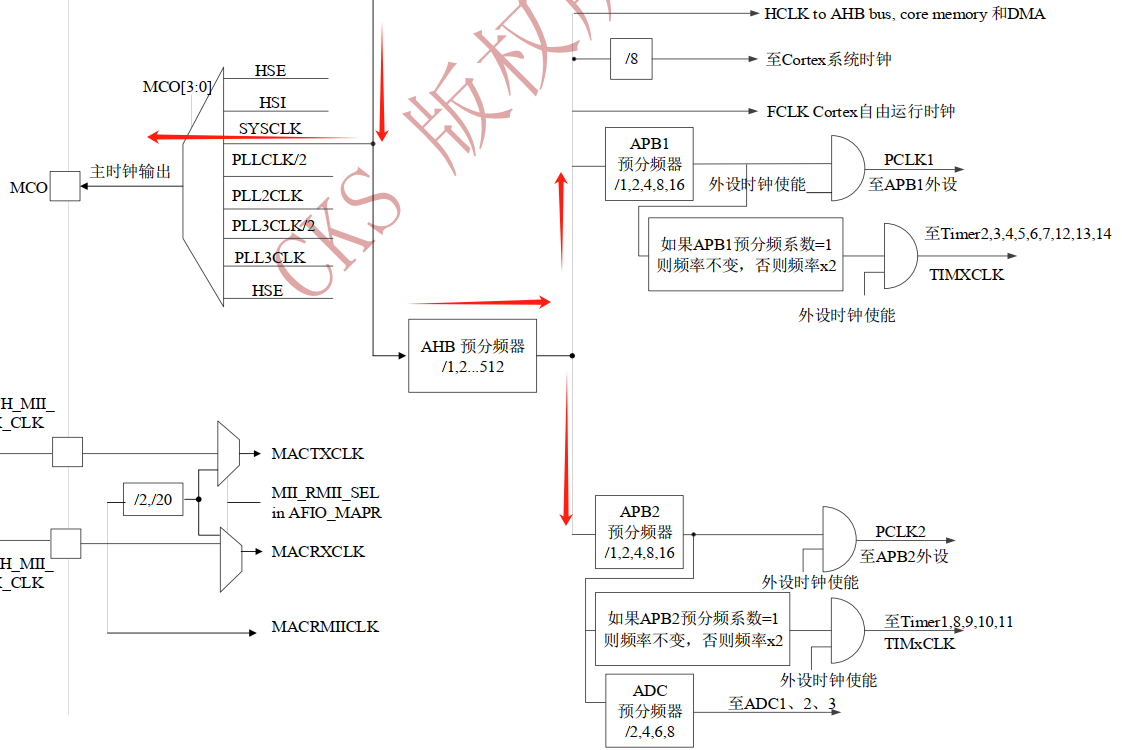

图2 APB频率生成流程

根据图1,产生SYSCLK时,内部HSI时钟经过二分频,输入PLLSCR模块,再通过PLLM倍频系数产生PLLCLK,即SYSCLK。

由图2可知,SYSCLK通过AHB预分频产生APB即HCLK等时钟系统。

配置寄存器

CKS32F107xx系列时钟配置寄存器

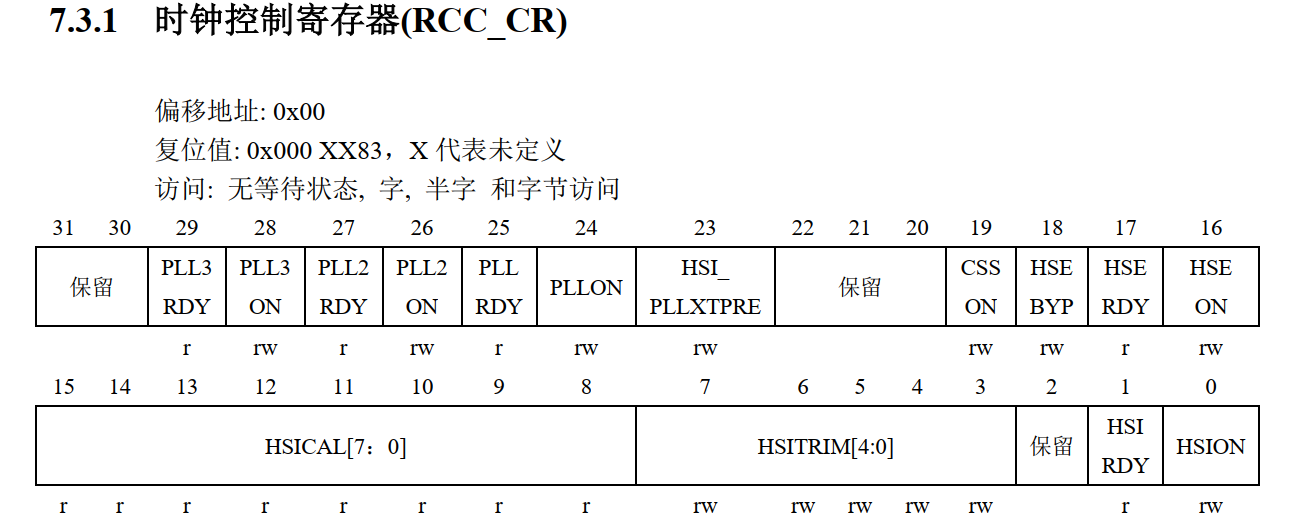

在使用HSI对系统时钟进行配置时,有两个较为重要的RCC寄存器,分别为RCC_CR、RCC_CFGR:

图3 RCC_CR寄存器

在RCC_CR寄存器中,我们需要关注如下几位:

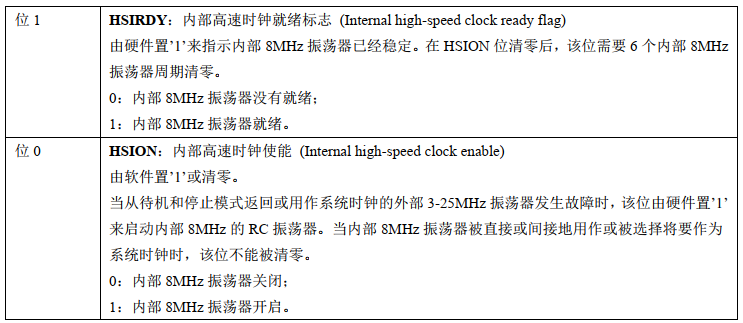

图4 HSI启动及状态寄存器

图5 PLL启动及状态寄存器

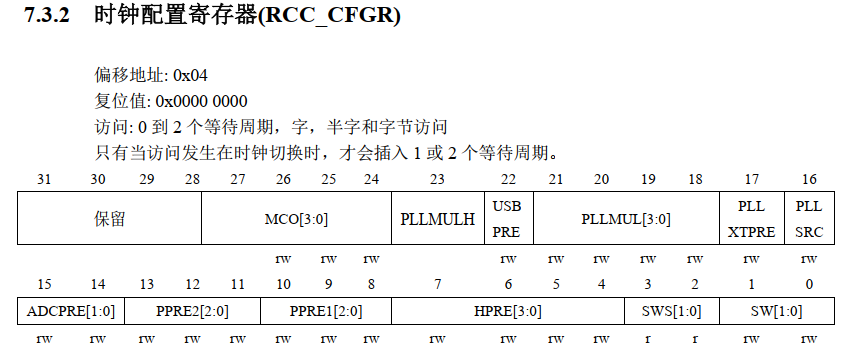

图6 RCC_CFGR寄存器

在RCC_CFGR寄存器中,我们需要关注如下几位:

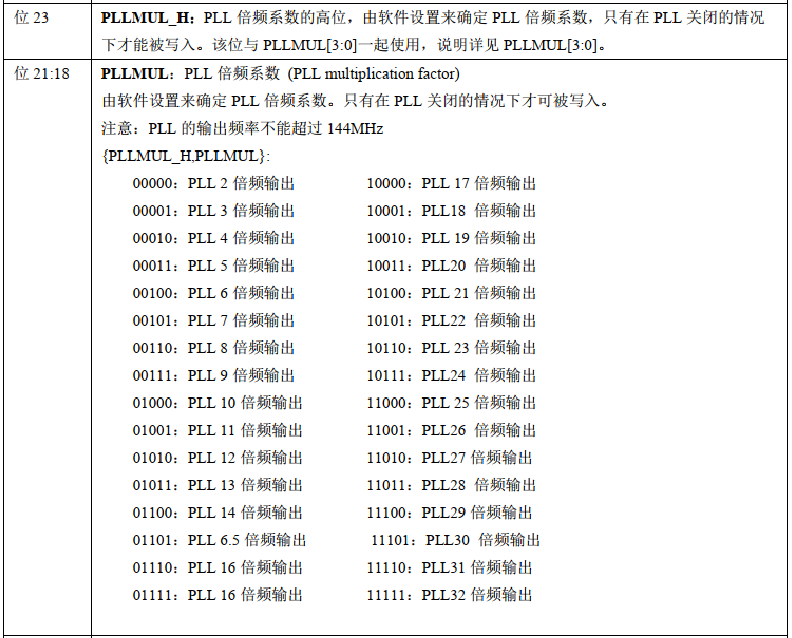

图7 PLL倍频系数位

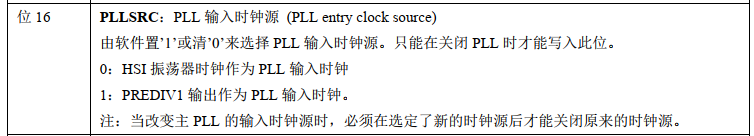

图8 PLL时钟源位

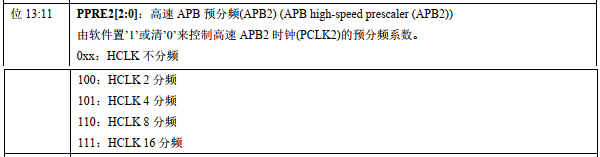

图9 APB2预分频位

图10 其他RCC_CFGR控制位

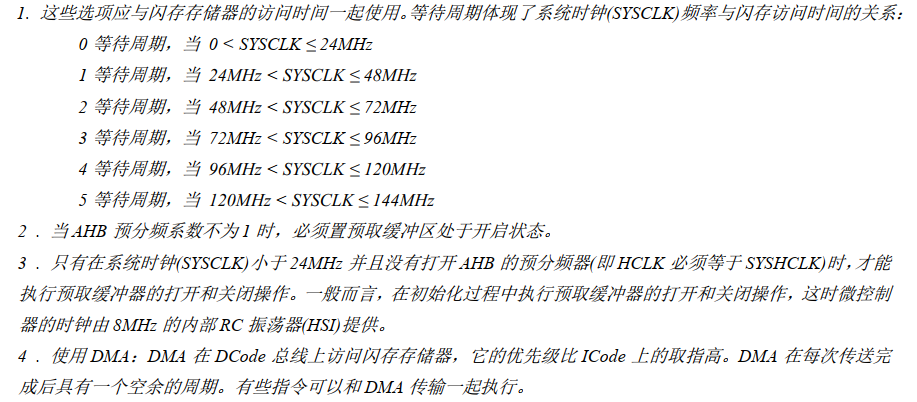

在对系统时钟进行初始化过程中,一般也会对闪存访问时间进行配置,如下为CKS32F107xx系列闪存访问时间与系统时钟的对应关系:

图11 闪存访问时间

CKS32F107xx系列时钟配置代码

依据上一章节中对寄存器的基本介绍,即可在函数SetSysClock()中对程序时钟进行相关配置,本文以HSI为时钟源,进行36MHz SYSCLK/HCLK/APB1/APB2配置。

/* SYSCLK, HCLK, PCLK2 and PCLK1 configuration ---------------------------*/

/* Enable HSI */

RCC->CR |= ((uint32_t)RCC_CR_HSION);

/* Wait till HSI is ready and if Time out is reached exit */

while((RCC->CR & RCC_CR_HSIRDY) == 0){}

/* Enable Prefetch Buffer */

FLASH->ACR |= FLASH_ACR_PRFTBE;

/* Flash 1 wait state */

FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_1;

/*AHB Prescaler set*/

RCC->CFGR |= (uint32_t)RCC_SYSCLK_Div1;

/* HCLK = SYSCLK */

RCC->CFGR |=(uint32_t)RCC_CFGR_HPRE_DIV1;

/* PCLK2 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;

/* PCLK1 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV1;

/* PLL configuration: PLLCLK = HSI / 2 * 9 = 36 MHz */

RCC->CFGR &= (uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLMULL);

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLMULL9);

/* Enable PLL */

RCC->CR |= RCC_CR_PLLON;

/* Wait till PLL is ready */

while((RCC->CR & RCC_CR_PLLRDY) == 0){}

/* Select PLL as system clock source */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

/* Wait till PLL is used as system clock source */

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08){}

来源:中科芯MCU

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。