作为MCU运行的基础,时钟是MCU各个模块工作时序的最小时间单位,推动MCU的各指令执行,是MCU选型的一个重要指标。CKS32F107xx系列MCU具有众多的外设,但并非所有的外设均需要系统时钟的高频率,并且高时钟频率将导致功耗增加、抗电磁干扰能力变弱,因此,CKS32F107xx系列MCU内部具备多个时钟源。本文将对CKS32F107xx系列时钟组成进行介绍,以帮助让用户对系统时钟了解。

CKS32F107系列时钟介绍

CKS32F107系列时钟树

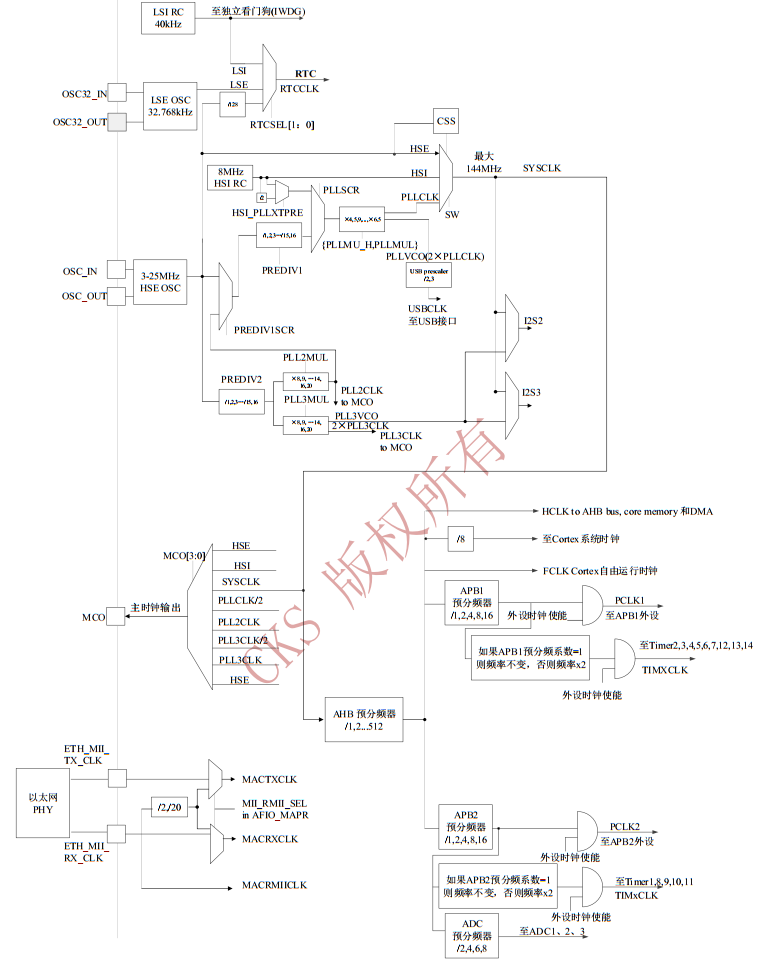

在CKS32F107xx系列MCU中,有HSI、HSE、LSI、LSE、PLL五个重要的时钟源。从时钟频率来分可以分为高速时钟源(HSI、HSE、PLL)和低速时钟源(LSI、LSE);从来源可分为外部时钟源(HSE、LSE)和内部时钟源(HSI、LSI、PLL);从功能应用配置划分可分为系统时钟(SYSCLK)、时钟安全系统(CSS)、独立看门狗时钟、RTC时钟。下图为CKS32F107xx系列MCU时钟树时钟树:

图1 CKS32F107系列MCU时钟树

HSE时钟

高速外部时钟信号(HSE)由以下两种时钟源产生:

●HSE外部晶体/陶瓷谐振器

●HSE用户外部时钟

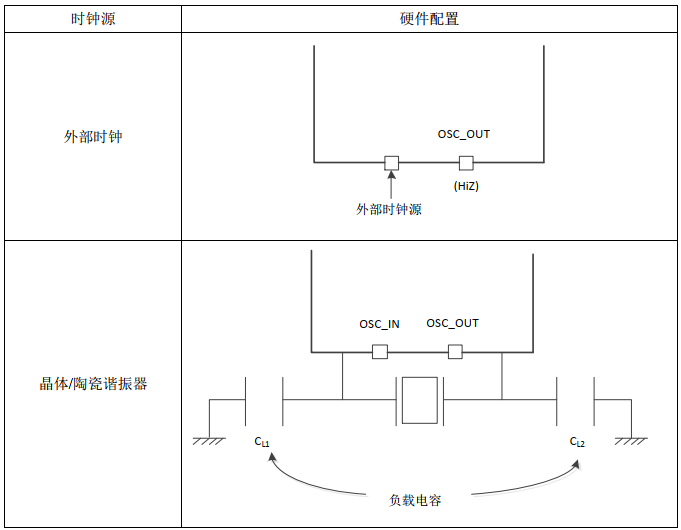

为了减少时钟输出的失真和缩短启动稳定时间,晶体/陶瓷谐振器和负载电容器必须尽可能地靠近振荡器引脚。负载电容值必须根据所选择的振荡器来调整。

图2 HSE时钟源

外部晶体/陶瓷谐振器(HSE晶振):

4~16Mz外部振荡器可为系统提供更为精确的时钟。相关的硬件配置可参考图1,在时钟控制寄存器RCC_CR中的HSERDY位用来指示高速外部振荡器是否稳定。直到这该位被硬件置’1’,才能使用HSECLK。如果在时钟中断寄存器RCC_CIR中允许产生中断,将会产生相应中断。

HSE晶振可以通过设置时钟控制寄存器里RCC_CR中的HSEON位被启动和关闭。

HSE用户外部时钟(HSE旁路):

在这个模式里,必须提供外部时钟。它的频率最高可达25MHz。用户可通过设置在时钟控制寄存器中的HSEBYP和HSEON位来选择这一模式。外部时钟信号(50%占空比的方波、正弦波或三角波)必须连到OSC_IN引脚,同时保证OSC_OUT引脚悬空。见图1。

HSI时钟

HSI时钟信号由内部8MHz的RC振荡器产生,可直接作为系统时钟,也可在不分频或2分频后作为PLL输入源。HIS RC振荡器能够在不需要任何外部器件的条件下提供系统时钟。它的启动时间比HSE晶体振荡器短。但是,即使在校准之后它的时钟频率精度仍较HSE晶振差。

PLL

主PLL以下述时钟源之一为输入,产生倍频的输出:

●HSI时钟

●HSI的二分频时钟

●HSE通过一个可配置分频器提供的时钟

●PLL2通过一个可配置分频器提供的时钟

PLL2和PLL3由HSE通过一个可配置的分频器提供时钟。必须在使能每个PLL之前完成PLL的配置(选择时钟源、预分频系数和倍频系数等),同时应该在它们的输入时钟稳定(就绪位)后才能使能。一旦使能了PLL,这些参数将不能再被改变。当改变主PLL的输入时钟源时,必须在选中了新的时钟源(通过时钟配置寄存器(RCC_CFGR)的PLLSRC位)之后才能关闭原来的时钟源。时钟中断寄存器(RCC_CIR),可以在PLL就绪时产生一个中断。

LSE时钟

LSE晶振是一个32.768kHz的低速外部晶体或陶瓷谐振器。它为实时时钟或者其他定时功能提供一个低功耗且精确的时钟源。

(1)外部晶体/陶瓷谐振器(LSE晶振)

LSE晶振通过在备份域控制寄存器(RCC_BDCR)里的LSEON位启动和关闭。在备份域控制寄存器(RCC_BDCR)里的LSERDY指示LSE晶体振荡是否稳定。在启动阶段,直到这个位被硬件置’1’后,LSE时钟信号才能被使用。如果在时钟中断寄存器里被允许,可产生中断请求。

(2)外部时钟源(LSE旁路)

在这个模式里必须提供一个32.768kHz频率的外部时钟源。可以通过设置在备份域控制寄存器(RCC_BDCR)里的LSEBYP和LSEON位来选择这个模式。具有50%占空比的外部时钟信号(方波、正弦波或三角波)必须连到OSC32_IN引脚,同时保证OSC32_OUT引脚悬空。

LSI时钟

LSI RC担当一个低功耗时钟源的角色,它可以在停机和待机模式下保持运行,为独立看门狗和RTC提供时钟。LSI时钟频率大约40kHz(在30kHz和60kHz之间)。进一步信息请参考数据手册中有关电气特性部分。

LSI RC可以通过控制/状态寄存器(RCC_CSR)里的LSION位来启动或关闭。在控制/状态寄存器(RCC_CSR)里的LSIRDY位指示低速内部振荡器是否稳定。在启动阶段,直到这个位被硬件设置为’1’后,该时钟才能使用。如果在时钟中断寄存器(RCC_CIR)里被允许,将产生LSI中断请求。

系统时钟(SYSCLK)选择

系统复位后,HSI振荡器被选为系统时钟。当时钟源被直接或通过PLL间接作为系统时钟时,它将不能被停止。当系统时钟从一个时钟源到另一个时钟源切换时,只有当目标时钟源准备就绪(经过启动稳定阶段的延迟或PLL稳定),才能进行切换,否则,系统时钟的切换不允许发生。在时钟控制寄存器(RCC_CR)的状态位会指示哪个时钟已经准备好了,哪个时钟目前被用作系统时钟。

时钟安全系统(CSS)

时钟安全系统可以通过软件被激活。一旦其被激活,时钟监测器将在HSE振荡器启动稳定后被使能,并在HSE时钟关闭后关闭。

如果HSE时钟发生故障,HSE振荡器被自动关闭,时钟失效事件将被送到高级定时器(TIM1的刹车输入端,并产生时钟安全中断CSSI,允许软件完成营救操作。此CSSI中断连接到内核的NMI中断(不可屏蔽中断)。

需要强调的是一旦CSS被激活,并且HSE时钟出现故障,CSS中断就产生,并且NMI(不可屏蔽的中断)也自动产生。NMI将被不断执行,直到CSS中断挂起位被清除。因此,在NMI(不可屏蔽的中断)的处理程序中必须通过设置时钟中断寄存器(RCC_CIR)里的CSSC位来清除CSS中断。

如果HSE振荡器被直接或间接地作为系统时钟,(间接的意思是:它被作为PLL输入时钟,并且PLL时钟被作为系统时钟),时钟故障将导致系统时钟自动切换到HSI振荡器,同时外部HSE振荡器被关闭。在时钟失效时,如果HSE振荡器时钟(被分频或未被分频)是用作系统时钟的PLL的输入时钟,PLL也将被关闭。

独立看门狗时钟

如果独立看门狗已经由硬件选项或软件启动,LSI振荡器将被强制在打开状态,并且不能被关闭。在LSI振荡器稳定后,时钟供应给IWDG模块。

RTC时钟

通过设置备份域控制寄存器(RCC_BDCR)里的RTCSEL[1:0]位,RTCCLK时钟源可以由HSE/128、LSE或LSI时钟提供。除非备份域复位,此选择不能被改变。

LSE时钟在备份域里,但HSE和LSI时钟不在备份域。因此:

(1)如果LSE被选为RTC时钟:只要VBAT维持供电,即使VDD供电被切断,RTC仍能工作。

(2)如果LSI被选为RTC时钟:如果VDD供电被切断,RTC不能工作。

(3)如果HSE时钟128分频后作为RTC时钟:如果VDD供电被切断或内部电压调压器被关闭(1.5V域的供电被切断),则RTC状态不确定。

时钟输出(MCO)

微控制器允许输出时钟信号到外部MCO引脚。相应的GPIO端口寄存器必须被配置为相应功能。以下8个时钟信号可被选作MCO时钟:

●SYSCLK

●HSI

●HSE

●PLL时钟的二分频

●PLL2时钟

●PLL3时钟的二分频

●XT13-25MHz外部晶振时钟(用于以太网)

●PLL3时钟(用于以太网)

时钟配置寄存器(RCC_CFGR)中的MCO[3:0]位控制。

以上就是CKS32F107xx系列MCU的介绍,在实际应用中,可根据使用外设情况,进行相关配置。

来源:中科芯MCU

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。