概 述

在进行电机类、电源类应用开发时,如何使用PWM定时器模块灵活、高效的实现所需 PWM波形的输出,是众多开发者关注的问题。在上篇文章里,我们介绍了PWM定时器模块内的一些概念,以及如何生成普通PWM的过程。本篇内容将继续介绍互补PWM、同步 PWM、错相 PWM以及PWM如何使用ACMP封波等内容。

互补PWM

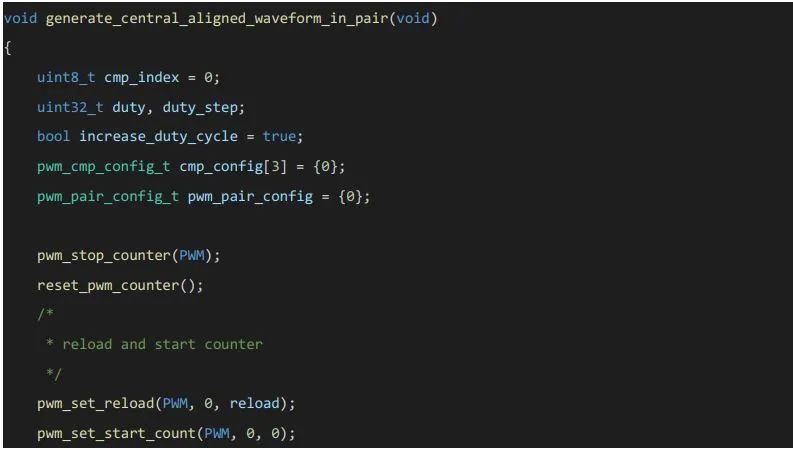

关于相同的代码部分,此处不再重复讲解,请参考《上篇》的普通PWM的讲解。

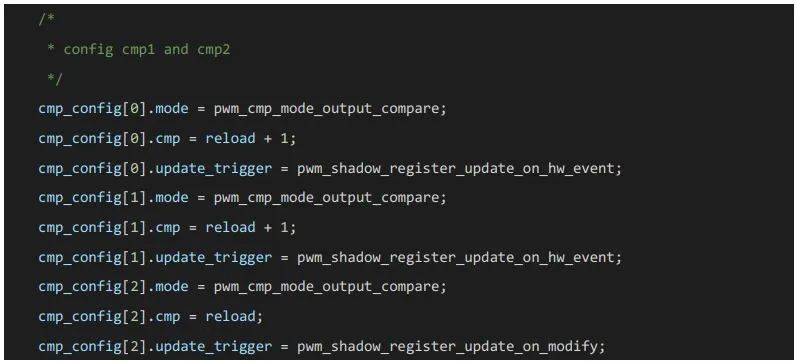

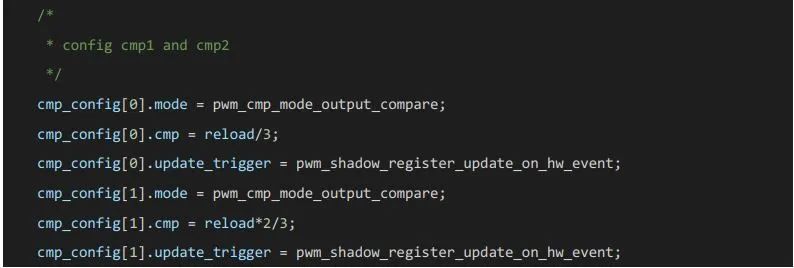

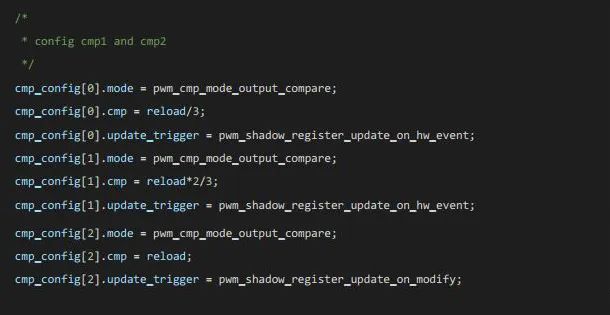

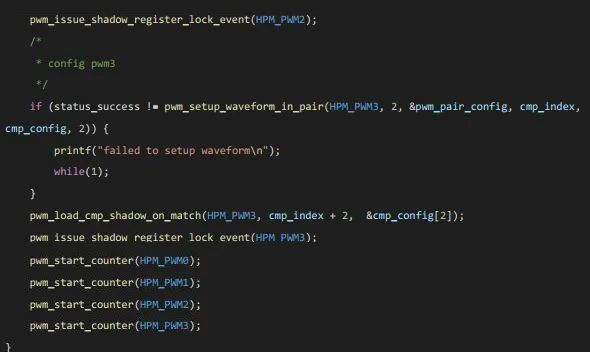

此处设置了 3 个比较器:cmp_config[0]与 cmp_config[1]用来生成中心对称 PWM,cmp_config[2]作为 PWM 影子寄存器的更新事件源,当 CNT 等于 cmp_config[2]时,影子寄存器写入寄存器内生效。

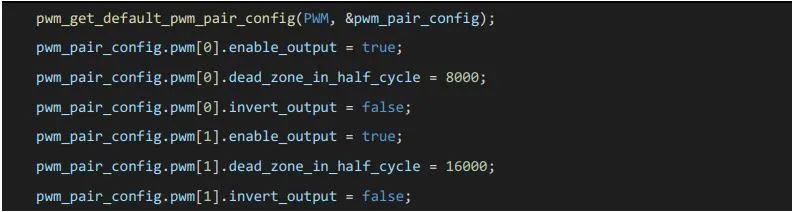

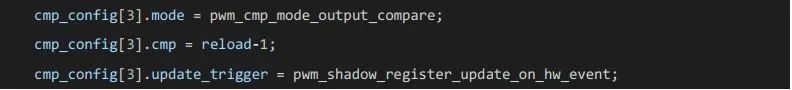

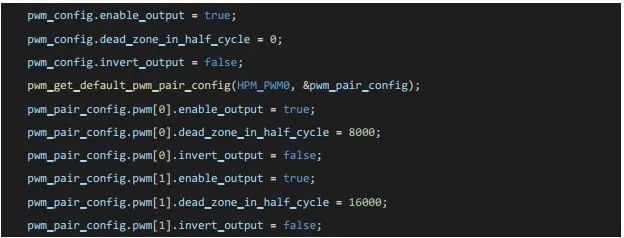

互补 PWM 对的配置,配置左死区宽度为 8000 个 half_clock,右死区宽度为 16000 个 half_clock。

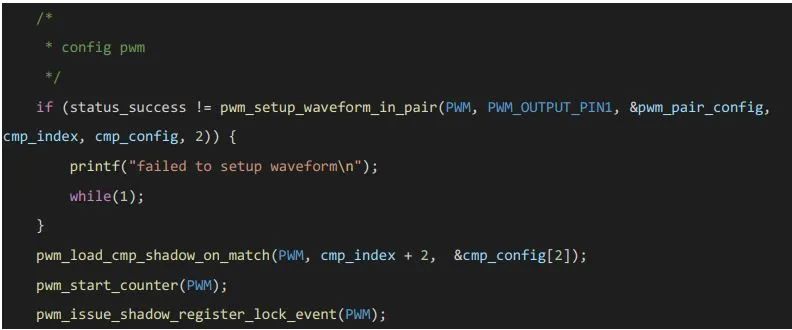

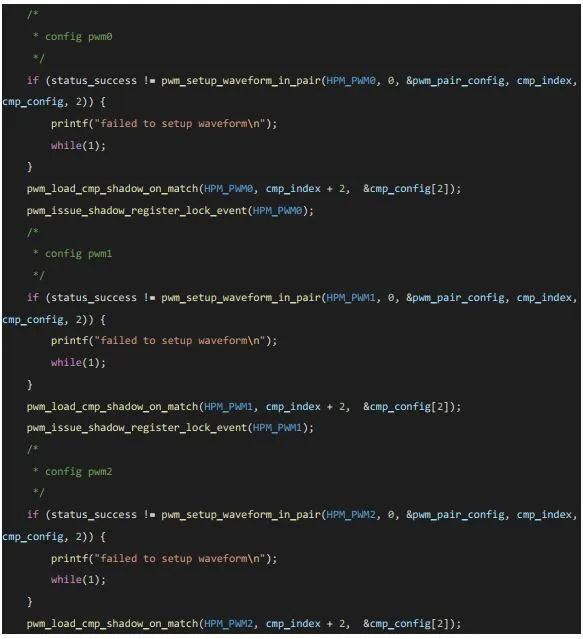

设置 cmp_config[2]作为 PWM 影子寄存器的更新事件源,启动计数器。

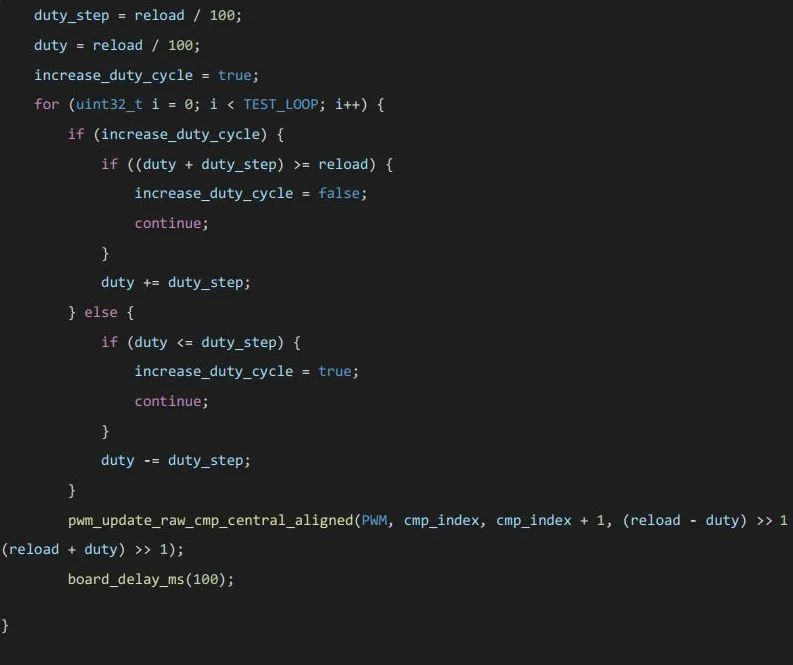

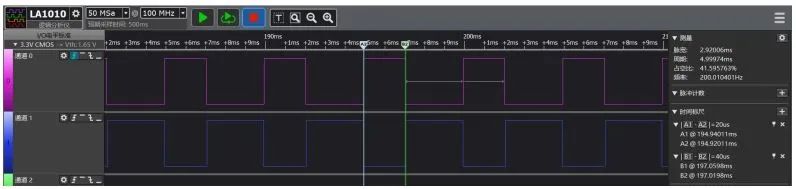

通过修改 CMP0 与 CMP1 的值,每 100ms 更新一次互补 PWM 占空比。运行结果如下:

同步PWM

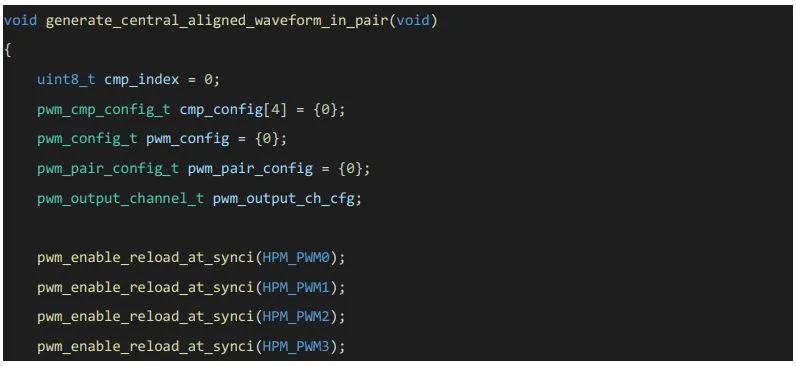

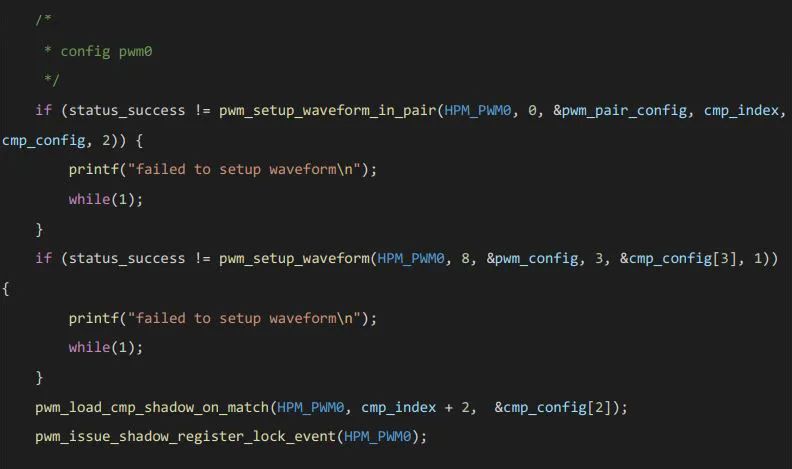

本节实验设计:使用 PWM0 的比较器比较事件去做 PWM1、PWM2、PWM3 的同步事件。故输出波形上看,PWM1、PWM2、PWM3 应完全同步,PWM0 与其则不同步。代码如下:

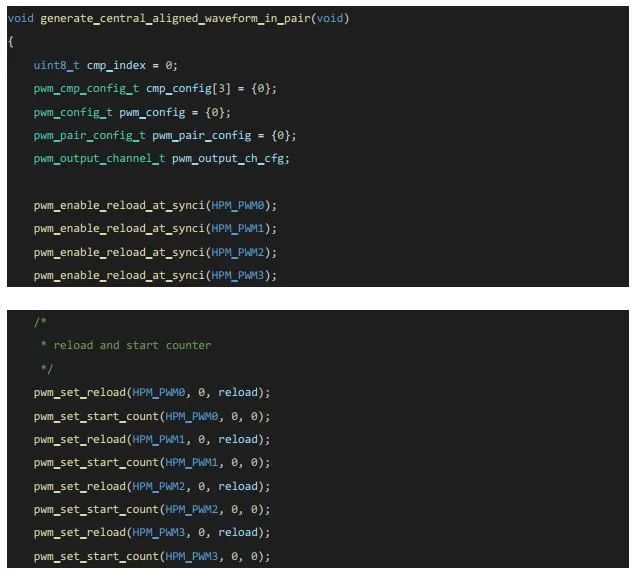

使能 4 个 PWM 定时器的 SYNCI 信号。

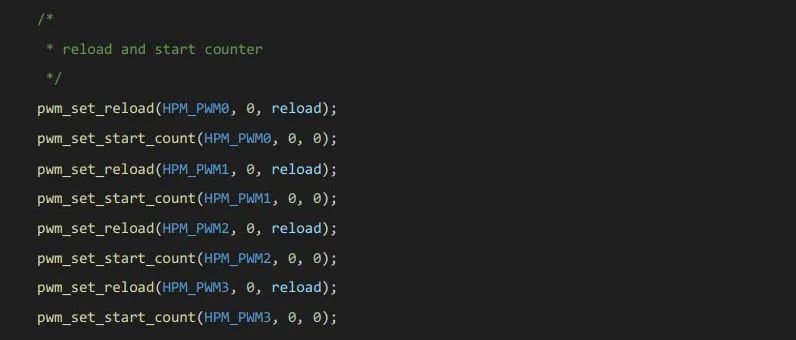

设置 STA 与 RLD。

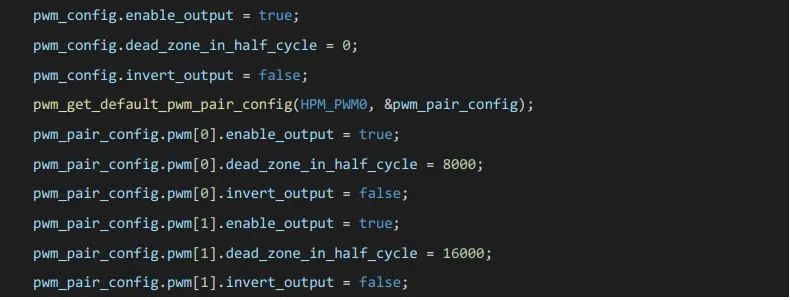

cmp_config[0]与 cmp_config[1]用来做中心对称 PWM 所需的比较器。

cmp_config[2]用来做使 PWM 影子寄存器生效的比较器。

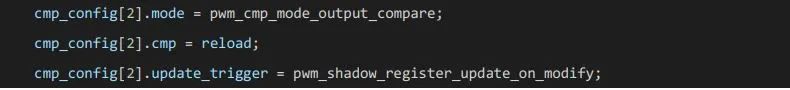

cmp_config[3]设置在 PWM0 CH8 上,用来产生比较事件,同步 PWM1、PWM2、PWM3。

互补 PWM 的死区设置与输出设置。

设置 PWM0 CH0 CH1 互补输出,同时设置 PWM1 CH8 使用 CMP3 产生比较事件。

设置 PWM1、PWM2、PWM3 互补输出。

启动计数器。

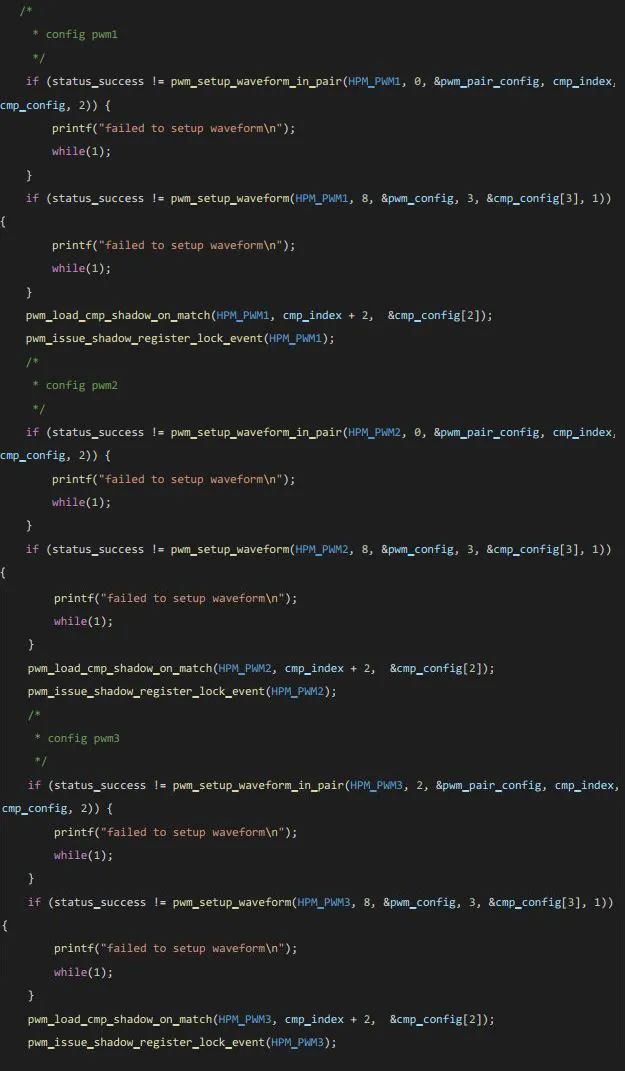

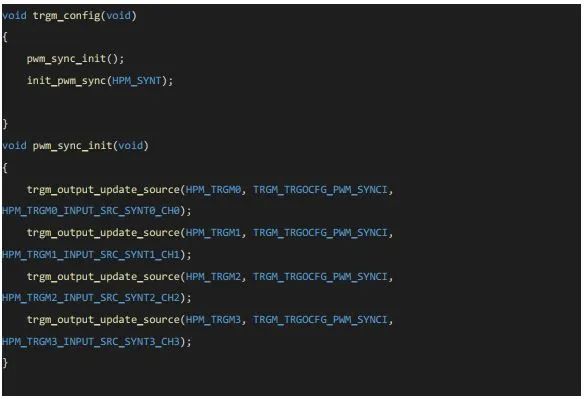

以下代码是对互联管理器的配置。配置 PWM0 CH8 的下降沿输出到TRGM0_OUTX0 上,同时 TRGM0_OUTX0 作为 TRGM1、TRGM2、TRGM3的输入,路由到 PWM1、PWM2、PWM3 的 SYNCI 信号上。

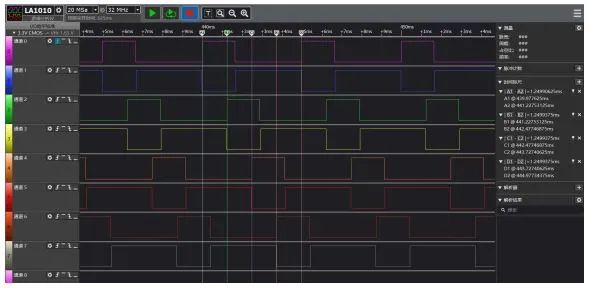

波形如下:

可见 PWM1、PWM2、PWM3 是完全同步的,PWM0 则与其有 20ns 的不同步。

错相 PWM

本节实验设计:使用 SYNT 实现 PWM0、PWM1、PWM2、PWM3 错相90°。代码如下:

以上代码请参考上文 “同步PWM” 章节的讲解,主要目的是生成 4 对互补PWM。

配置 TRGM,将 SYNT CH0 的比较事件路由到 PWM0 的 SYNCI 信号上,将 SYNT CH1 的比较事件路由到 PWM1 的 SYNCI 信号上,将 SYNT CH2 的21 / 24先楫半导体比较事件路由到 PWM2 的 SYNCI 信号上,将 SYNT CH3 的比较事件路由到PWM3 的 SYNCI 信号上。

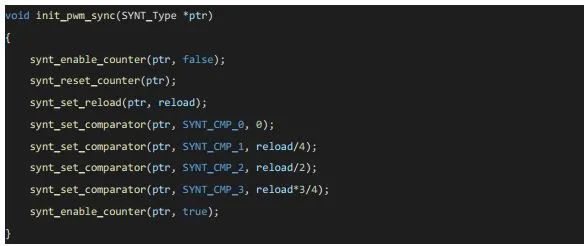

配置 SYNT,分别设置 SYNT CH0 比较器比较值为 0,SYNT CH1 比较器比较值为 reload/4,SYNT CH2 比较器比较值为 reload/2,SYNT CH4 比较器比较值为 reload*3/4。

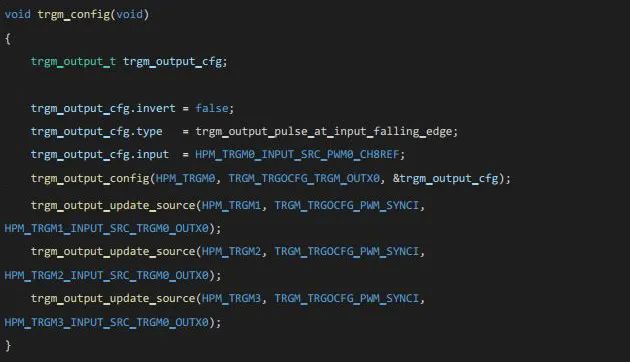

波形如下:

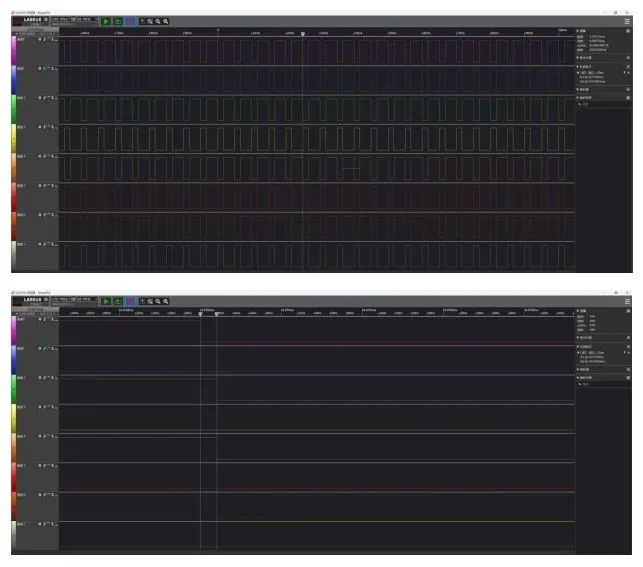

PWM+ACMP 封波

本节实验设计:使用两个片上 ACMP 对目标模拟电压进行监控,当电压超过 1.65V 时停止 PWM 输出。其基本思路为,将 ACMP 的输出信号通过互联管理器 TRGM 路由到 PWM 的内部 Fault 信号上,当 Fault 信号有效时 PWM波停止输出(故障保护功能)。

代码如下:

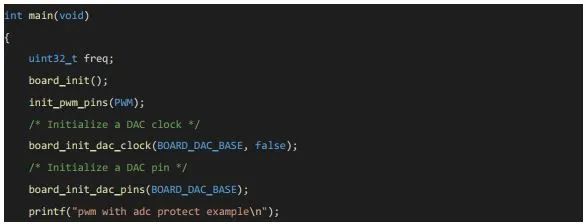

初始化 PWM 引脚,初始化 DAC 时钟与引脚(使用 DAC 输出模拟电压到ACMP 上模拟过压)。

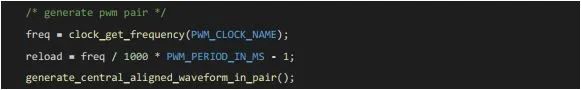

输出互补 PWM 波。

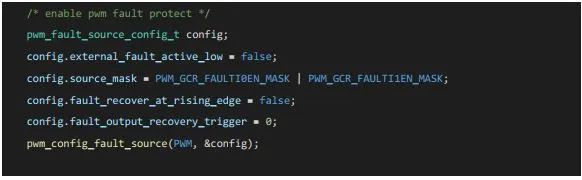

设置 Fault 信号高电平有效;使能 FaultI0 与 FaultI1 有效(PWM 共 4 内2 外 fault 信号,哪些信号生效可选)。

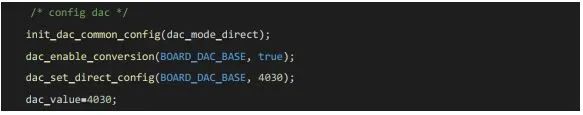

设置 DAC 输出为直接模式,12bit DAC 输出范围 0~4095,4030 约为3.247V。该部分代码请直接参考 DAC 例程。

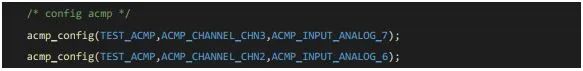

配置 ACMP,使能 ACMP2 与 ACMP3。

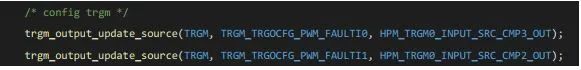

配置互联管理器,将 ACMP2 与 ACMP3 的输出信号路由到 PWM 的FaultI0 与 FaultI1 上去。

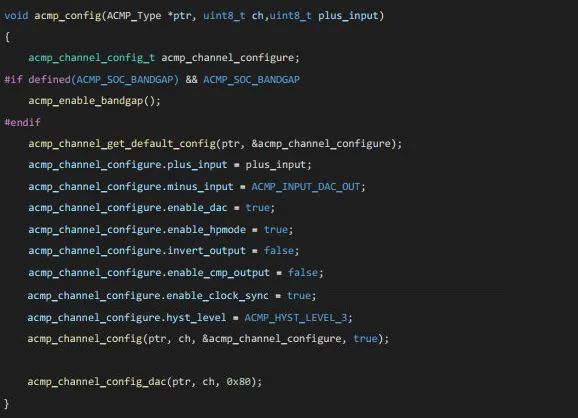

acmp_config 函数源码如下:

代码中将 ACMP 的正极输入选择为 IO 引脚,负极输入选择为 ACMP 内部专用 DAC,参考电压设置为 0x80,即 1.65V。

当 IO 引脚电压 3.247V 时(来自于外设 DAC 输出),ACMP 正极电压超过负极电压 1.65V,ACMP 输出有效,为高电平;经过互联管理器路由到PWM 的 Fault 信号上;由于 PWM 模块内配置了 Fault 信号为高电平有效,因此此时 Fault 信号有效,PWM 波形停止输出。

当 IO 引脚电压 0V 时(将引脚与 GND 短接),ACMP 正极电压未超过负极电压 1.65V,ACMP 输出无效,PWM 波形正常输出。

小 结

本文首先介绍了 PWM 定时器内各模块的基本概念与功能,而后对 PWM的使用由浅入深依次以代码实例进行讲解。可以看到,PWM 的使用只要配置好 STA、RLD、CMPx、影子寄存器等即可实现输出;如果有同步需求或与其它外设协同使用需求,则主要通过互联管理器 TRGM 的配置进行实现。

比较经典的例程还包括使用 PWM 触发 ADC 采样,先楫半导体 SDK 中已经有完整的实例与代码,各位开发者可以到官网下载研究,并欢迎大家多多交流。

来源:先楫半导体HPMicro

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。