【资料下载】PCB布局布线设计要点

PCB布局布线是产品设计中的重要一步,PCB布局布线的好坏将直接影响电路的性能。电子书《PCB布局布线设计要点》涵盖PCB布局布线的相关基本原理和设计技巧,并结合具体实例说明如何把这些技巧应用于实际设计之中从而有助于改善系统的整体性能。

PCB布局布线是产品设计中的重要一步,PCB布局布线的好坏将直接影响电路的性能。电子书《PCB布局布线设计要点》涵盖PCB布局布线的相关基本原理和设计技巧,并结合具体实例说明如何把这些技巧应用于实际设计之中从而有助于改善系统的整体性能。

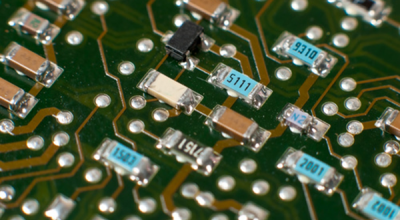

本文详细说明在设计混合信号PCB的布局时应考虑的内容。本文将涉及元件放置、电路板分层和接地平面方面的考量。本文讨论的准则为混合信号板的布局设计提供了一种实用方法,对所有背景的工程师应当都能有所帮助。

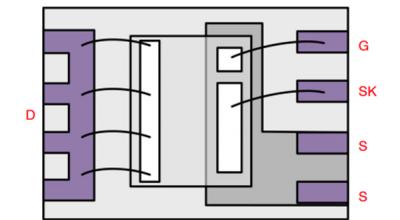

本设计文档其余部分引用的布线示例将使用含有源极开尔文连接引脚的 GaNFET 封装。

本文将简单介绍NCP51820及利用 NCP51820 设计高性能 GaN 半桥栅极驱动电路的 PCB 设计要点。

电子设备的灵敏度越来越高,这要求设备的抗干扰能力也越来越强,因此PCB设计也变得更加困难,如何提高PCB的抗干扰能力成为众多工程师们关注的重点问题之一。

在如今的印刷电路板设计中,双数据速率(DDR)存储器非常普遍。许多设计都会用到DDR存储器配置的不同版本,这需要在布局中使用特定的布线模式。

PCB基本设计流程一般包括:前期准备->PCB结构设计->PCB布局->布线->布线优化和丝印->网络和DRC检查和结构检查。

在PCB设计中,电磁兼容性(EMC)及关联的电磁干扰(EMI)历来是让工程师们头疼的两大问题,特别是在当今电路板设计和元器件封装不断缩小、OEM要求更高速系统的情况下。本文给大家分享如何在PCB设计中避免出现电磁问题。

本文,从射频界面、小的期望信号、大的干扰信号、相邻频道的干扰四个方面解读射频电路4大基础特性,并给出了在PCB设计过程中需要特别注意的重要因素。

变化的信号(例如阶跃信号)沿传输线由A到B传播,传输线C-D上会产生耦合信号,变化的信号一旦结束也就是信号恢复到稳定的直流电平时,耦合信号也就不存在了,因此串扰仅发生在信号跳变的过程当中,并且信号沿的变化(转换率)越快,产生的串扰也就越大。