【下载】通过 MPLAB® Harmony v3 使用 SAMC MCU上的 Σ−Δ 模数转换器 ( SDADC)

本文档介绍了 ATSAMC21N 器件中配置为差分模式的 SDADC,SDADC 结果会显示在控制台上。

MCU是Microcontroller Unit(微控制器单元)的缩写,它是一种集成了中央处理器(CPU)、存储器(ROM、RAM)、输入/输出端口(I/O)、定时器(Timer)、串行通信接口(UART、SPI、I2C等)和其他外围设备控制器的单个芯片。MCU通常用于嵌入式系统中,用于控制各种电子设备和系统。

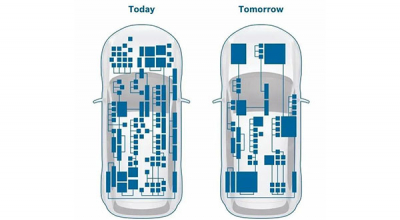

由于其集成度高、体积小、功耗低以及成本相对较低等特点,MCU被广泛应用于各种嵌入式系统中,例如智能家居设备、医疗设备、汽车电子系统、工业自动化等。MCU的选择通常基于应用的需求,如处理性能、功耗、外设接口等因素。

本文档介绍了 ATSAMC21N 器件中配置为差分模式的 SDADC,SDADC 结果会显示在控制台上。

2020年的世界格局使得半导体电子行业受到疫情、中美贸易等外部环境等的影响深远、意义重大。

对于使用直接存储器访问(Direct Memory Access,DMA)进行数据传输操作的应用程序,当其运行在具有可高速缓存存储区的单片机(MCU)上时,难以避免地会出现高速缓存一致性问题。

本视频介绍了Microchip提供的基于MPLAB®代码配置器(MCC)的16位自举程序,支持16位PIC24 MCU和dsPIC33 DSC。

作为中国电子信息产业风向标的“第九届中国电子信息博览会(2021CITE)”于2021年4月9日在深圳福田区会展中心拉开帷幕,本届博览会集中展示包括智慧家庭、智能终端、人工智能、智能制造、高端芯片、新型显示、虚拟现实及增强现实、智能网联汽车、5G和物联网等代表电子信息产业未来发展的核心内容。

增添小型、低成本的微控制器(MCU)以实现简单的辅助处理功能,可以对许多电路的设计产生助益。

今天跟大家分享一位嵌入式工程师的项目开发感悟,写得非常的接地气,学习和开发过程可以进行相应参考!

本文档介绍了如何将直接存储器访问控制器(XDMAC)与基于 Arm® Cortex®-M7 的 MCU(SAM E70)上的四通道串行外设接口(Quad Serial Peripheral Interface,QSPI)搭配使用,还介绍了如何使用MPLAB® Harmony v3 软件框架实现应用程序,并评估了使用或不使用 XDMAC 时 QSPI 读写操作的性能。

自举程序是一段代码,用于将应用程序代码(固件)编程或重新编程到单片机的内部闪存,而无需使用外部编程器或调试器。

通用汽车表示将生产一款“缺芯”皮卡,并且强调即使未来芯片供应恢复正常,由于工艺原因这些车辆出厂后也无法返厂改装,缺芯会永久性影响车辆行驶里程。