详析开关电源中的电感电流测量

开关电源通常使用电感来临时储能。在评估这些电源时,测量电感电流通常有助于了解完整的电压转换电路。

开关电源通常使用电感来临时储能。在评估这些电源时,测量电感电流通常有助于了解完整的电压转换电路。

本文中,DigiKey深入探讨电源拓扑结构与设计要点,涵盖线性电源与开关电源特点,及SMPS多种类型,助力精准选型与高效设计。

为什么稳定的开关模式电源仍会产生振荡?非常稳定的开关模式电源(SMPS)仍可能由于其在输出端的负电阻而产生振荡。在输入端,可以将SMPS看作一个小信号负电阻。其与输入电感和输入端电容一起可形成一个无阻尼振荡电路。

输入过压是由电网负载的巨大波动引起的。例如,在用电高峰期,电压通常较低,而在设备关闭时,电压则较高。

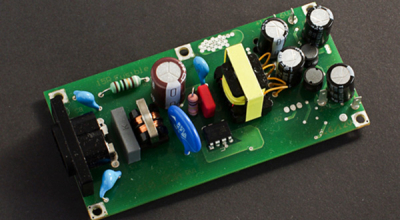

对于功率转换器,寄生参数最小的热回路PCB布局能够改善能效比,降低电压振铃,并减少电磁干扰(EMI)。

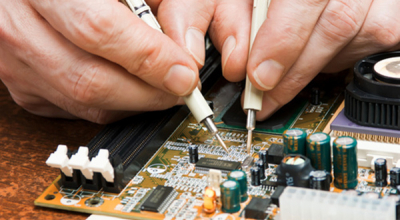

在设计开关模式电源时,优化电路板布局是一个重要的方向。合理布局可以确保开关稳压器保持稳定工作,并尽可能降低辐射干扰和传导干扰(EMI)。

优化电路板布局是开关电源设计中的一个关键。良好的布局可确保开关稳压器的稳定运行,并将辐射干扰和传导电磁干扰(EMI)降至最低。

在高压或低压输入下开机(包含轻载,重载,容性负载),输出短路,动态负载,高温等情况下,通过变压器(和开关管)的电流呈非线性增长,当出现此现象时,电流的峰值无法预知及控制,可能导致电流过应力和因此而产生的开关管过压而损坏。

大多数电子系统都需要在供能电压和需要供电的电路电压之间进行某种转换。

非隔离型开关电源一般有三种基本工作方式,降压型、升压型、极性反转型三种,而其他的都是这三种形式转换而来,例如反激式、正激式、推挽式、半桥式、全桥式。