雅特力AT32 MCU通过IEC 60730功能安全认证,为家电产品提供安全保障

近日,雅特力AT32 MCU安全库顺利通过IEC 60730功能安全认证,为家电产品提供安全质量保证。国际公认的测试、检验和认证机构SGS为雅特力科技颁发了IEC 60730认证证书,彰显了雅特力科技在家电控制领域的卓越品质和技术实力,也为其在全球范围内的广泛应用奠定了坚实基础。

近日,雅特力AT32 MCU安全库顺利通过IEC 60730功能安全认证,为家电产品提供安全质量保证。国际公认的测试、检验和认证机构SGS为雅特力科技颁发了IEC 60730认证证书,彰显了雅特力科技在家电控制领域的卓越品质和技术实力,也为其在全球范围内的广泛应用奠定了坚实基础。

近日,雅特力与SEGGER共同宣布J-Link仿真调试器与Flasher在线烧录器全面支持AT32 MCU产品,SEGGER工具链的加持使AT32 MCU开发如虎添翼。

嵌入式系统应用市场广泛,早已遍及日常生活,随着产品需求复杂度的提升,32位MCU开发难度也随之增加,如何降低开发成本,缩短开发周期,是所有嵌入式开发人员的共同课题。

触摸屏介绍

过去商务办公成立必不可少的四机设备,复印机、打印机、扫描机和传真机等,为缩短人力作业时间,提升工作效率,各种办公设备也逐步推出更符合人性化需求,多功能一体机也是其中一大变革之一。多功能一体机主要是将打印、复印、扫描和传真等不同用途的机器整合为一机,并结合联网功能。

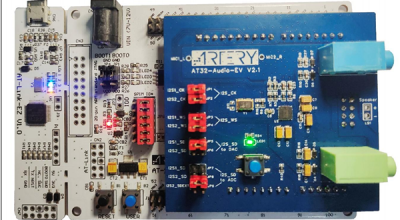

本文基于此开源模型和代码,在AT32 MCU上对KWS效果进行展示。

在HID中,以及在HOGP的延伸中,定义了两个角色,这些角色是HID主机和HID设备。HID设备一次只能主动连接到单个HID主机;然而一个HID主机可以连接到多个HID设备。有关主机和设备如何交互的细节,请参阅HOGP规范中的第3章HID设备需求和第4章HID主机需求和行为。

本应用笔记介绍了如何将FreeMODBUS协议栈移植到AT32F43x单片机方法。本文档提供的源代码演 示了使用Modbus的应用程序。单片机作为Modbus从机,可通过RS485或RS232与上位机相连,与 Modbus Poll调试工具(Modbus主机)进行通讯。

AT32提供在VSCode下开发、编译、下载、调试解决方法。只需安装所需要的软件工具并简单配置即可使用。本指南所使用的所有软件,目前都是开源的。

二维码由于自身设计特点,可包含更多的信息量,编码信息范围更广,并且由于二维码具有一定的校验功能等。同时还具有对不同行的信息自动识别功能、以及处理图形旋转变化点,二维码译码更加准确,其误码率为千万分之一。下图为QR二维码构造框图。