MindSDK应用基础——ADC模块样例

MindSDK为MM32主流的微控制器,实现了一组ADC样例工程。本文通过讲解ADC模块的样例工程,介绍ADC模块的功能和用法。关于ADC模块对应的驱动程序,以及ADC外设模块硬件的实现细节,可具体查阅MindSDK工程的源文件,以及MM32微控制器(例如MM32F5270)的用户手册。

MindSDK为MM32主流的微控制器,实现了一组ADC样例工程。本文通过讲解ADC模块的样例工程,介绍ADC模块的功能和用法。关于ADC模块对应的驱动程序,以及ADC外设模块硬件的实现细节,可具体查阅MindSDK工程的源文件,以及MM32微控制器(例如MM32F5270)的用户手册。

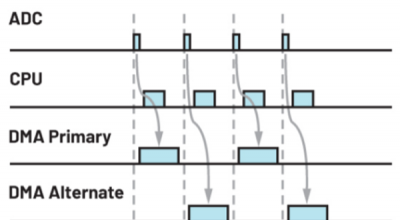

在上一讲单通道ADC电压采集的基础上,本节主要介绍CKS32F4xx系列产品基于DMA传输的ADC多通道电压采集转换实现。

该文档包含了HPM6750_ADC_EVK板的介绍,设计细节,使用方式,以及硬件设计图等内容。

ADC外设是12位的逐次逼近型(SAR)模拟数字转换器,可以将模拟信号转换成数字信号。

模数转换器(ADC)的主要功能是将模拟量转换为数字量,方便MCU进行处理。下面以CW32L083为例介绍CW系列的模数转换器的特点和功能,并提供演示实例。

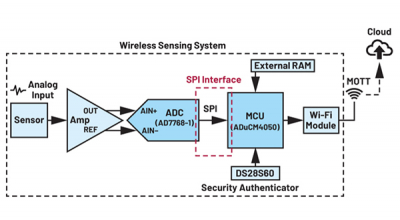

本文描述了设计MCU和ADC之间的高速串行外设接口(SPI)关于数据事务处理驱动程序的流程,并简要介绍了优化SPI驱动程序的不同方法及其ADC与MCU配置。

本文描述了设计MCU和ADC之间的高速串行外设接口(SPI)关于数据事务处理驱动程序的流程,并简要介绍了优化SPI驱动程序的不同方法及其ADC与MCU配置。本文还详细介绍了SPI和直接存储器访问(DMA)关于数据事务处理的示例代码。最后,本文演示了在不同MCU(ADuCM4050、MAX32660)中使用相同驱动程序时ADC的吞吐率。

一、限幅滤波法

1、方法:

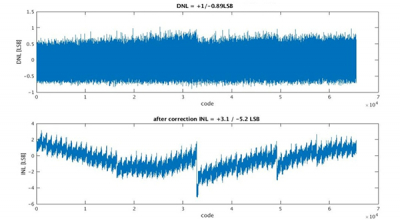

本文将为大家展示国产芯片HPM6000系列ADC性能出色的测试结果并为您提供了与HPM6000系列微控制器的模数转换器ADC相关的外部电路设计建议。

本视频包含如下内容:

1.N32 MCU ADC特性

2.SAR ADC工作原理

3.ADC获取最佳精度

4.ADC使用注意事项