基于ST STM32G474的500W全桥移相零电压切换直流-直流转换器数字电源方案

随着科技的迅速发展,电子产品日新月异与半导体制程技术进步,电子产品逐渐要求体积小且效率高。

随着科技的迅速发展,电子产品日新月异与半导体制程技术进步,电子产品逐渐要求体积小且效率高。

意法半导体的STEVAL-NRG011TV评估板可帮助设计人员为LED 和 OLED 电视快速开发200W 数字电源和适配器,能效和待机能耗满足严格的法规要求。

与碳化硅 (SiC)FET 和硅基FET 相比,氮化镓 (GaN) 场效应晶体管 (FET) 可显著降低开关损耗和提高功率密度。

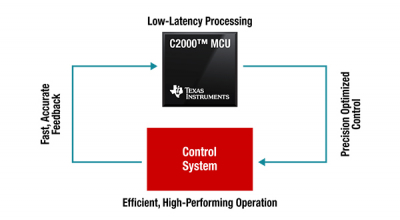

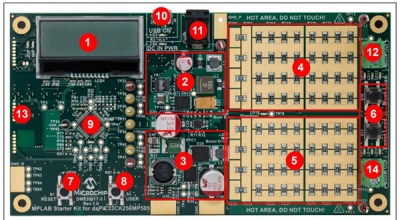

现代电源正朝着更小巧、更高效率、更灵活、更便宜的方向发展。而随着数字信号控制器(DSC)被集成到开关电源设计中,这些理想的增强特性已得到实现。工具包中提供的电路板用于介绍和演示Microchip SMPS系列器件的功能和特性。

简单的引脚可配置数字模块为高性能的FPGA、DSP、ASIC和存储器提供了最高的功率密度和效率

AVCC:模拟部分电源供电;AGND:模拟地

DVCC:数字部分电源供电;DGND:数字地

本数据手册介绍了dsPIC33EPXXXGS70X/80X系列DSC。这是一款带互连的高速PWM、 ADC、 PGA和比较器且适用于数字电源应用的16位数字信号控制器。

Microchip Technology Inc. Alex Dumais