贸泽开售支持新一代创新网络的 NXP LX2 QorIQ Layerscape处理器

该系列处理器采用最多16个Arm® Cortex®-A72处理器核心,具有可扩展的数据路径加速逻辑,以及用于支持存储、网络、无线基础设施、军事、航空航天和电信等应用的网络和总线接口。

处理器,也被称为中央处理器(Central Processing Unit,CPU),是计算机系统中的关键组件之一,负责执行计算机程序中的指令,控制计算机的各个部分,并处理数据。

该系列处理器采用最多16个Arm® Cortex®-A72处理器核心,具有可扩展的数据路径加速逻辑,以及用于支持存储、网络、无线基础设施、军事、航空航天和电信等应用的网络和总线接口。

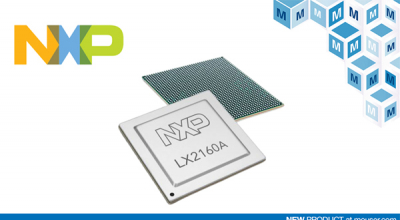

5月18日,平头哥发布旗下玄铁系列新款处理器—玄铁907,该处理器对开源RISC-V架构进行优化设计,兼顾高性能及低功耗特点,可应用于MPU(微处理器)、智能语音、导航定位、存储控制等领域,据透露,该处理器已向多家企业授权。

英特尔®酷睿™ i9-11980HK最高可达到5.0GHz的频率,能够为游戏玩家、内容创作者和专业商务人士提供超凡性能。

随着对嵌入式系统的要求越来越高,作为其核心的嵌入式微处理器的综合性能也受到日益严峻的考验。

昨日,英特尔面向全球正式发布第11代智能英特尔®酷睿™S系列台式机处理器。

• 全新Arm Mali-C52和Mali-C32图像信号处理器(ISP)提供一流的图像质量、完整的软件包以及全套校准和调校工具。

• 为各种日常设备提供更高图像质量,包括无人机、智能家庭助理和安全、以及网络(IP)摄像机。

• 新的应用程序现已能利用Arm Iridix技术的独有功能优势;该技术已经在超过20亿台设备上得以证实。

近年来随着物联网、车用电子及智慧家居等需求兴起,电源管理与微控制器(MCU)等晶片用量逐步攀升,已经排挤其他部分8吋芯片产能的投片量,根据TrendForce光电研究(WitsView)最新观察指出,晶圆代工厂相继提高8吋厂IC代工费用。

目前全球需要越来越大的计算能力来处理像人工智能和机器学习这样的资源密集型工作负载,IBM公司以其最新一代Power芯片 - Power9进入了竞争。该公司打算向第三方制造商和包括Google在内的云供应商出售该芯片。与此同时,它发布了一款由Power9芯片和AC922芯片组成的新电脑,并打算在IBM云上提供该芯片的计算服务。IBM表示它通常把技术作为一个完整解决方案推向市场。

业界首款基于ARM®Cortex®-M7的跨界处理器,达到3020 CoreMark得分和1284DMIPS,并可在600 MHz时提供20纳秒的中断延迟 - 现已上市,价格在同类解决方案中极具优势

一、

STM32的AD转换,可以将转换任务组织为两个组:规则组和注入组。

在任意多个通道上以任意顺序进行的一系列转换构成成组转换。