DDR5系统管理引入了一种全新的边带总线,其正式名称为JESD403-1 JEDEC模块边带总线。DDR5标准的开发正由JEDEC和MIPI联盟合作进行。

在引入这种全新应用的情况下,该应用所用到的SPD集线器、PMIC和微控制器需要在确保协议合规性的基础上实现高度集成。因此,瑞萨开发了一种结合瑞萨SPD5集线器SPD5118、瑞萨PMIC、温度传感器和新款瑞萨RA RA2E2组的解决方案,以实现符合JEDEC JESD403和MIPI I3C BasicSM要求的边带总线操作。另一方面,这些关键的瑞萨设备已通过MIPI I3C BasicSM的全面认证,并且该系统还能够向后兼容旧版JEDEC I2C实施。

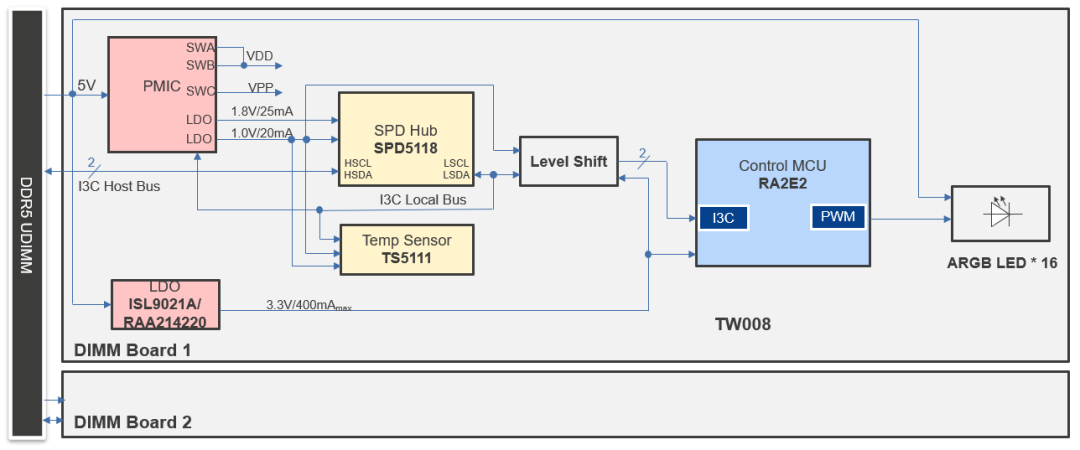

DDR5 DIMM边带总线和主机总线的简要架构

瑞萨DDR5解决方案附带原型套件,可配合上述的总线和电源布局架构使用,并在RA I3C总线的前端采用了电平移动电路,以满足JESD403-1的特定总线电压要求。客户可以通过他们的SDRAM模块充分利用此集成套件,从而加速产品发布计划。

管理总线协议

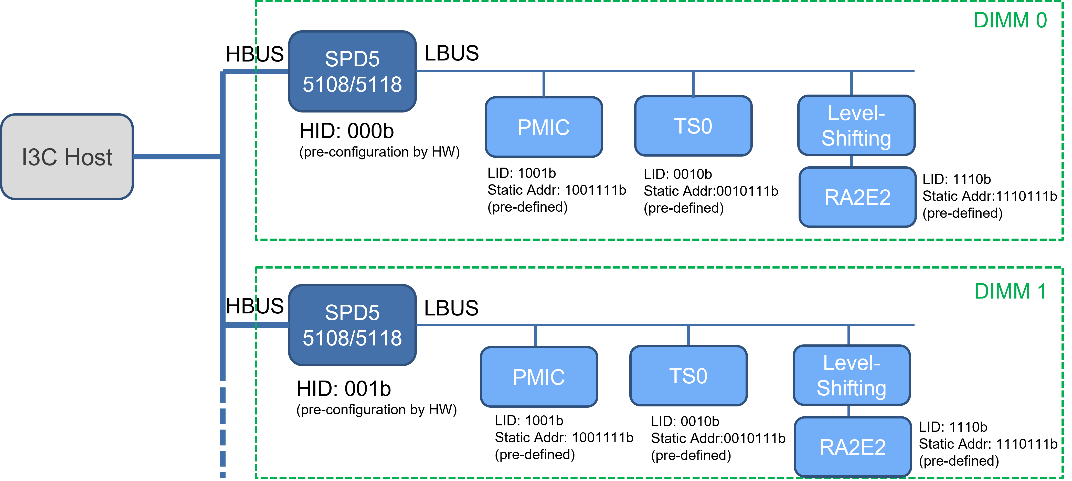

边带总线采用特定的结构化寻址方案(如下文简述)来识别DIMM以及DIMM上的设备。因此,I3C基础的ENTDAA和基于PID的地址计算方案并不需要强制执行。基于此情况,SPD集线器通过两个模式处理地址计算和HID分配,而DIMM上能够以I3C基础模式运行的设备应为JEDEC SETHID CCC和SETAASA CCC提供支持。

在JEDEC I2C模式中(默认通电),通信(以DIMM上的设备为目标从属设备)由主机发出启动条件开始,后接7位从属地址和一个读/写字位。通信过程中,作为首个接收器的SPD集线器将替换寻址DIMM的从属地址的LSB 3bits(HID)并转发到本地总线,不包括0x7E的广播地址。SPD集线器借助精密电阻检测HID/DIMM_ID并辅助HID分配。

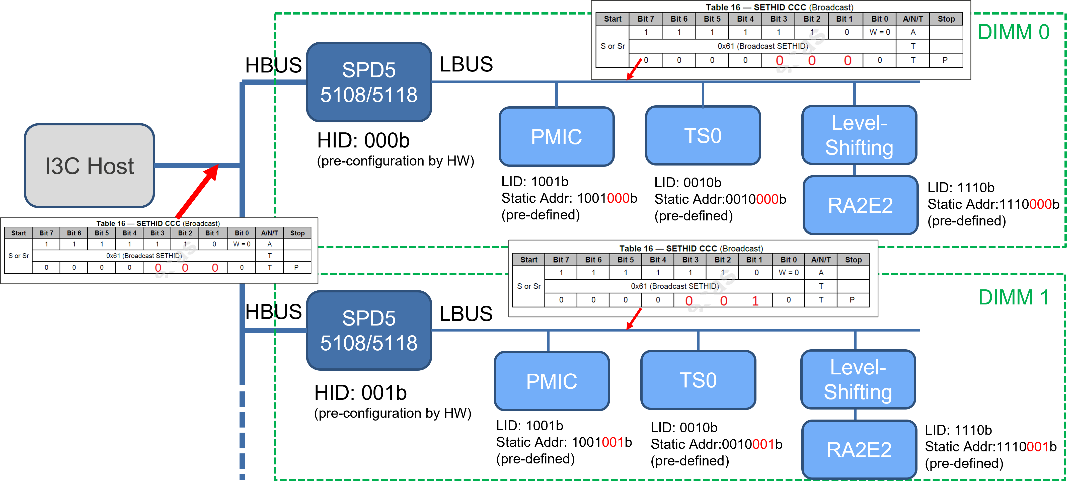

JEDEC I3C模式将一直生效,直至作为边带总线上首个接收器的SPD集线器接收到JEDEC SETHID CCC为止。一旦集线器检测到JEDEC SEHID CCC,集线器便会停止HID数位翻转,并将传入的7位从站地址按原样透明地传送到本地总线中。在此操作之后,DIMM上所有从SPD集线器接收SETHID CCC的I3C设备应更新其静态地址分配,并等待SETAASA CCC完成地址分配以进入I3C基础操作。

下图对上述两种模式的操作说明进行了汇总。

在收到JEDEC SETHID CCC之前I2C模式默认通电

接收到JEDEC SETHID CCC时,进入I3C模式

RA2E2组包含全面通过MIPI I3C BasicSM认证的I3C接口,可向后兼容旧版JEDEC I2C实施,设计师能够简化硬件设计,同时轻松而顺畅地实现从旧版I2C平台到I3C平台的转移。

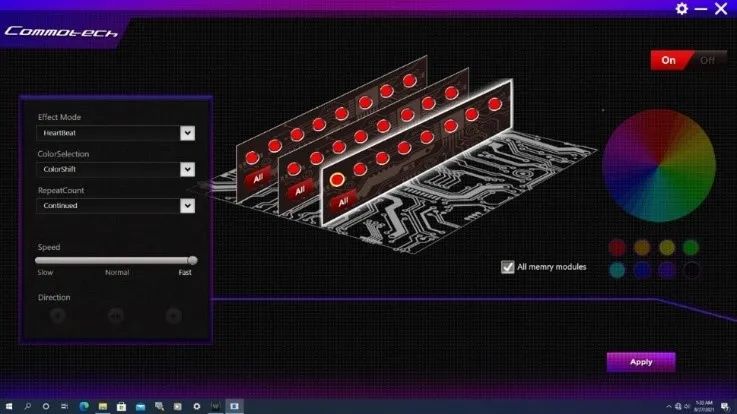

DDR5 ARGB LED控制实施

RA2E2组在尺寸仅为4.00mm×4.00mm的24引脚HW四方扁平无引脚(HWQFN)封装中提供6通道的通用PWM定时器。借助硬件支持,可以通过最大化可控ARGB LED阵列的数量来拓展照明效果的选项。

演示和验证

作为MIPI联盟的成员和较早采用MIPI I3C Basic SM和JEDEC JESD 403-1的先行者,瑞萨解决方案的边带总线运行和协议合规性验证已通过Prodigy I3C协议分析器和模拟器完成,可支持MIPI I3C Basic V1.0, V1.1规格。此外,瑞萨解决方案能够向后兼容SM总线,以满足英特尔目前对LED照明控制的DDR4和DDR5结构要求,而瑞萨的第三方合作商也将提供包括H/W、F/W和S/W在内的全套解决方案,从而改善整体开发环境。

来源:瑞萨MCU小百科

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。