一、SCG简介

系统时钟发生器(SCG)是MCU中的重要模块,它能够为芯片提供多个灵活的时钟源,并支持各种时钟输出选项,实现对芯片内部各个模块的时钟供应。CKS32K148的时钟生成电路提供了各种时钟分频器和选择器,允许不同的模块以该模块特定的频率运行,而时钟生成逻辑实现了可以独立关闭的模块特定时钟门控,从而能够优化芯片性能以满足低功耗的需求。本文将围绕CKS32K148的SCG模块展开介绍,以帮助用户对系统时钟的生成与使用进行了解。

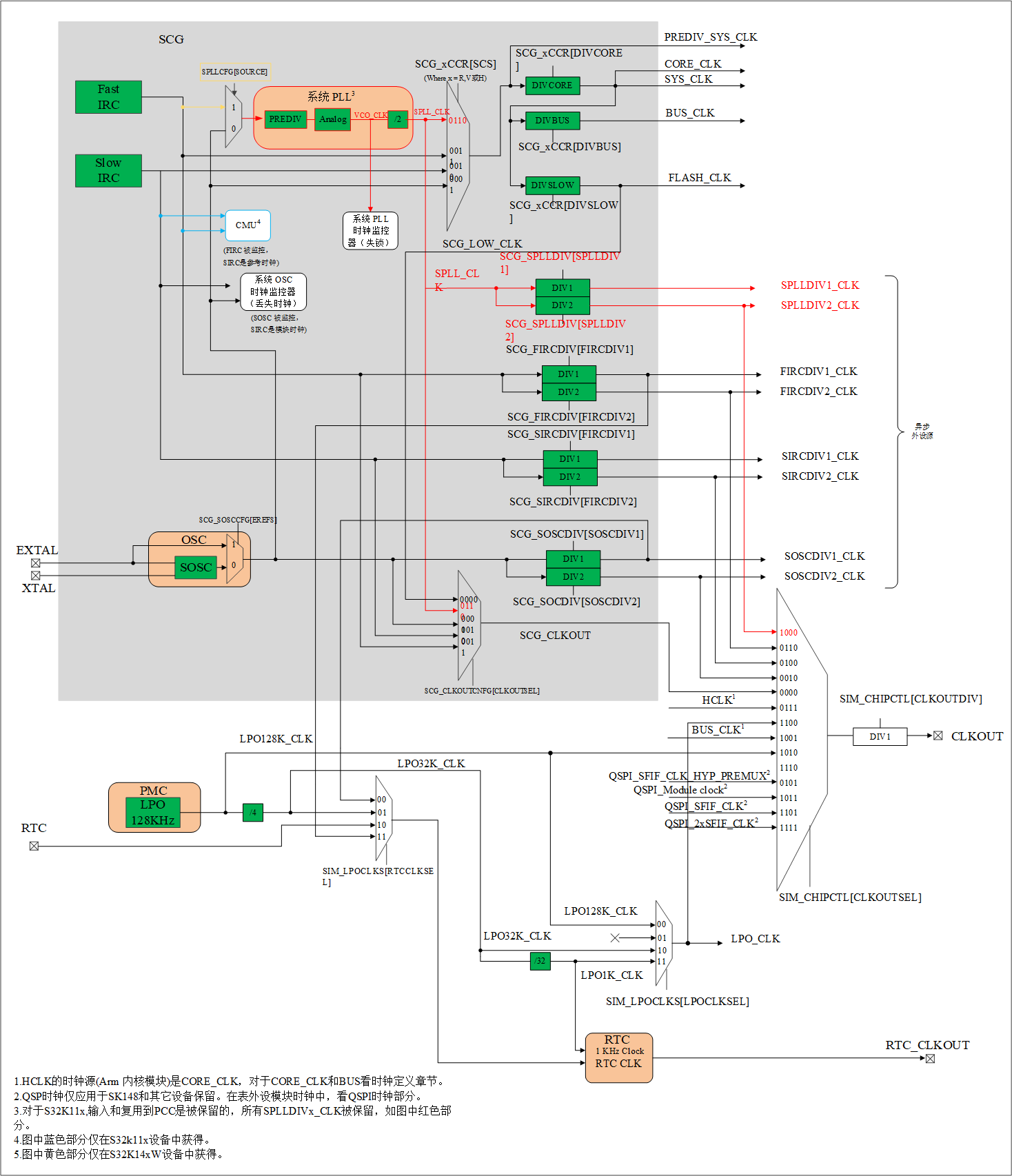

二、时钟树

对于CKS32K148,SCG模块包含四个可用作MCU系统时钟源的可选时钟:

内部快参考时钟(FIRC)

内部慢参考时钟(SIRC)

系统晶振时钟(SOSC)

系统锁相环(SPLL)

其中,SOSC可由内部晶振或外部参考时钟产生,而SPLL由SOSC参考时钟倍频后产生。系统时钟源将用于为内核、总线和FLASH提供时钟,除此之外,上述四种时钟在经过可编程分频器后输出的时钟信号可为外设提供时钟。

下图为CKS32K148的时钟树,其中灰色区域为系统时钟发生器(SCG)模块。

图1 CKS32K148时钟树

1、FIRC时钟

内部快参考时钟(FIRC)是芯片内部产生的频率为48MHz的时钟,它能够提供高频稳定的内部时钟信号,可作为MCU系统时钟源,也可作为其他片上外设的时钟源。FIRC有两个可编程分频器FIRCDIV1_CLK和FIRCDIV2_CLK,分频器的时钟输出也可作为异步时钟源应用于部分外设模块。

FIRC的使能由寄存器(SCG_FIRCCSR)中的标志位FIRCEN、FIRCVLD和FIRCREGOGG共同控制,只有在这些标志位均正确置位且FIRC模拟模块有一个时钟输出时,FIRC时钟有效。需要注意的是,若FIRCEN在时钟切换期间被写,则写指令执行前,应该先读回和确认。

2、SIRC时钟

内部慢参考时钟(SIRC)是芯片内部产生的频率为8MHz的时钟,它能够提供低频稳定的内部时钟信号,通常用于作为低功耗模式下的系统以及其他片上外设的时钟源。SIRC同样有两个可编程分频器SIRCDIV1_CLK和SIRCDIV2_CLK,其时钟输出可作为异步时钟源应用于部分外设模块。需要注意的是,对于部分需要高频时序控制和高速接口的外设,SIRC无法作为时钟源对其进行同步和控制,在使用这些模块时应注意时钟源的选择。

SIRC的使能由寄存器(SCG_FIRCCSR)中的标志位SIRCEN和SIRCVLD共同控制,只有在这些标志位均置‘1’时,SIRC时钟有效。若SIRCEN在时钟切换期间被写入同样应先读回和确认。除通用情况下的使能,在低功耗模式和停止模式下,SIRC的使能由标志位SIRCLPEN和SIRCSTEN分别控制。

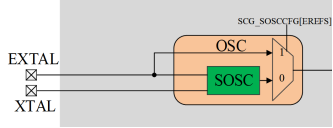

3、SOSC时钟

系统晶振时钟(SOSC)是由内部晶振或外部参考时钟产生的频率为4-40MHz的时钟,它能够提供精确稳定的时钟信号,通常用于为SPLL提供时钟信号,也可直接作为系统以及其他片上外设的时钟源。SOSC的可编程分频器为SOSCDIV1_CLK和SOSCDIV2_CLK,输出信号可用于作为外设异步时钟源。SOSC时钟源支持两档频率范围,可以通过寄存器(SCG_SOSCCFG)中的标志位RANGE来选择,‘10’对应中频范围4MHz至8MHz,‘11’对应高频范围8MHz至40MHz。

SOSC时钟源的选择可通过寄存器(SCG_SOSCCFG)中标志位 EREFS控制,置‘1’时使用的是内部OSC晶振,置‘0’时使用的是外部参考时钟。通常情况下,SOSC选用内部OSC晶振来作为时钟源,但需要注意的是,与内部参考时钟不同,这里的内部晶振信号并非在芯片内部直接产生,而是通过外接晶体振荡器的方式将时钟信号输入SOSC的xtal。而当选择外部参考时钟作为时钟源时,允许使用外部晶振、陶瓷谐振器或信号发生器等多种方式来产生外部参考时钟,生成的外部参考时钟信号通过连接OSC_IN引脚输入extal。

图2 SOSC时钟生成

SOSC的使能由寄存器(SCG_SOSCCSR)中的标志位SOSCEN和SOSCVLD共同控制,在这些标志位均置‘1’,并经过4096 个时钟周期计数后,SOSC被视为有效。若SOSCEN在时钟切换期间被写入,应先读回和确认。

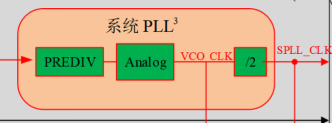

4、SPLL时钟

系统锁相环(SPLL)的内部由压控分频器、相位/频率检测器和整数循环滤波模块构成,它以SOSC作为参考时钟,通过对参考时钟信号的倍频和同步,提供了高精度、高稳定性和频率可调的时钟信号,是实现高性能、高稳定性系统的重要时钟源。SPLL通常作为MCU系统时钟源使用,也可作为其他片上外设的时钟源。它的两个可编程分频器分别为SPLLDIV1_CLK和SPLLDIV2_CLK,分频器的时钟输出可作为异步时钟源应用于部分外设模块。

对于SPLL的输出时钟频率,可根据下式计算获得:

SPLL_CLK = (VCO_CLK)/2

VCO_CLK = SOSC_CLK/(PREDIV + 1) *(MULT + 16)

其中,PREDIV和MULT的值可在寄存器(SCG_SPLLCFG)中的相应标志位处进行配置。

图3 SPLL时钟生成

SPLL的使能由寄存器(SCG_SPLLCSR)中的标志位SPLLEN和SPLLVLD共同控制,只有在这些标志位均置‘1’时,SPLL被视为有效。需要注意的是,虽然SPLL有自己的时钟错误标志位SPLLERR,但由于SPLL以SOSC为参考时钟,当寄存器(SCG_SOSCCFG)中的标志位SOSCERR已经置位时,即使SPLL时钟出现错误,SPLLERR将不会置位。同时,若程序检测到出现OSC 时钟错误(SOSCCSR[SOSCERR]),SPLLVLD位将被清零。

除此之外,SPLLVLD位仅适用与在初始化后验证SPLL是否被锁,其工作原理是通过一个锁检测电路来完成锁检测,以三个连续采样时钟检测的结果判断该时钟是否有效。当SPLL频率超出参考范围(见数据手册中的Dunl)时,将生成参考时钟的三个连续未被锁定样本,可判断为SPLL失锁,SPLLVLD位将被清零。

三、时钟输出(MCO)

SCG模块可输出到外部MCO引脚的时钟信号可分为两类。一类是在寄存器(SCG_CLKOUTCNFG)中通过标志位CLKOUTSEL控制的输出信号,能够以SCGCLKOUT_CLK的形式被选择输出到MCO引脚的时钟源信号:

FIRC_CLK

SIRC_CLK

SOSC_CLK

SPLL_CLK

另一类是在寄存器(SIM_CHIPCTL)中通过标志位CLKOUTSEL选择的输出信号,可直接输出到MCO引脚,包括:

内核时钟(CORE_CLK)

总线时钟(BUS_CLK)

外设时钟:SPLLDIV2_CLK、FIRCDIV1_CLK、FIRCDIV2_CLK、SIRCDIV2_CLK、SOSCDIV1_CLK、SOSCDIV2_CLK

输出上述时钟信号时,相应的GPIO端口寄存器必须被复用为CLKOUT功能。

四、系统时钟(SYSCLK)选择

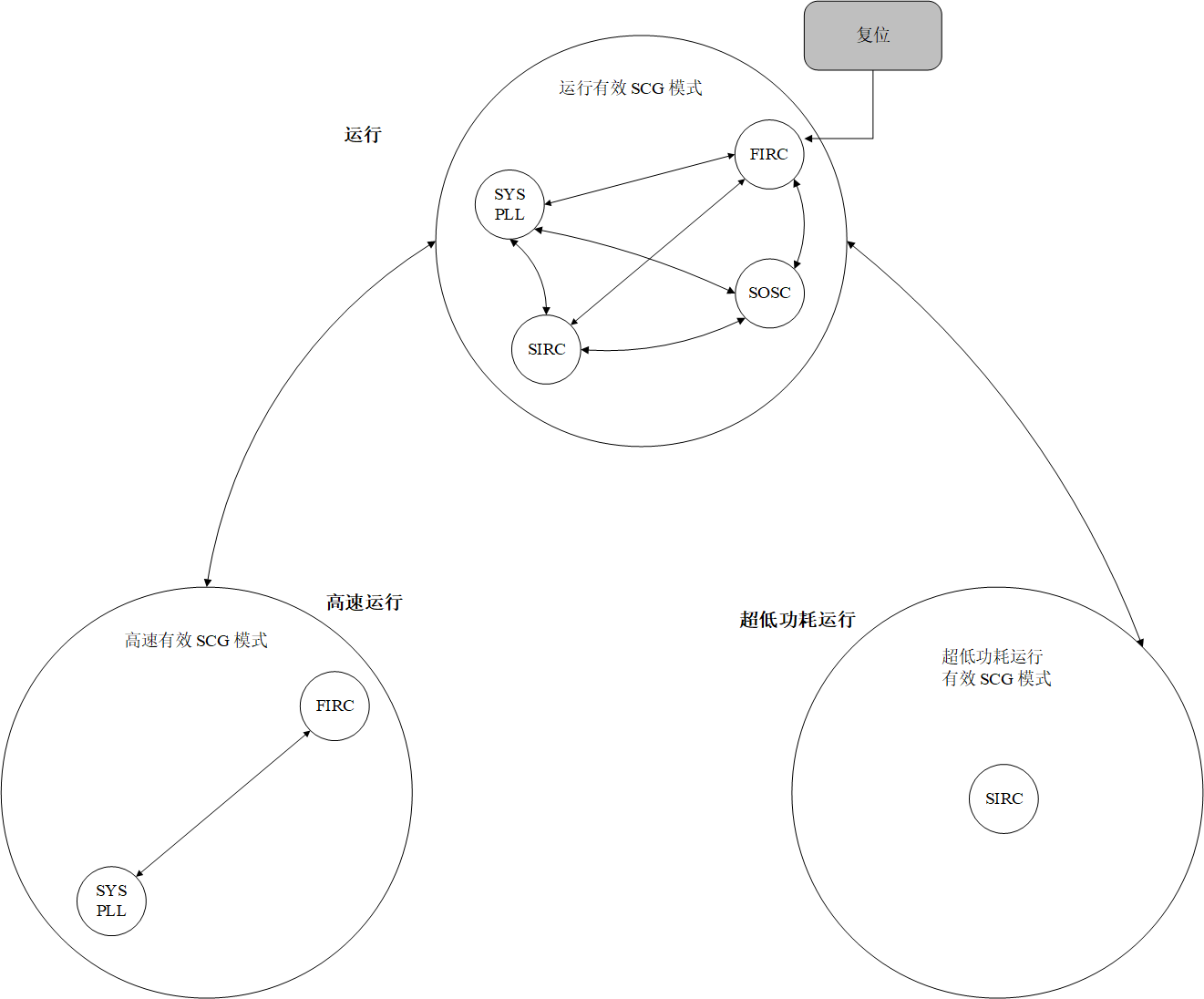

在前文中提到,SCG中包含四种可作为系统时钟源的可选时钟,但需要注意,在不同的系统工作模式下,并非所有的时钟都可作为系统时钟源。

在RUN模式下,可使用SPLL或SCG参考时钟(SIRC,FIRC和SOSC)作为MCU系统时钟源;在HSRUN模式下,可使用SPLL或FIRC作为MCU系统时钟源;在VLPRUN模式下,仅可使用SIRC作为MCU系统时钟源。

上述不同模式下的时钟源选择由寄存器(SCG_xCCR)中的标志位SCS控制。同时,被选择的时钟源需在自身对应的(SCG_xxxxCSR)寄存器中将标志位xxxxSEL置‘1’,才可被视为有效时钟源。

下图为SCG有效模式切换图,概括了不同模式下可使用的系统时钟源以及不同模式之间的切换关系。

图4 SCG有效模式切换图

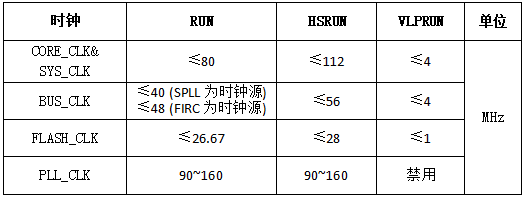

五、SCG时钟工作频率范围

在不同的工作模式下,系统对于不同的内部时钟存在安全工作频率范围的限制,以保证系统的正常工作。下表为SCG内部时钟在不同工作模式下的安全工作频率范围汇总。

表1 SCG内部时钟安全工作频率

SCG寄存器配置以及相关示例请期待下期微课堂,感谢大家!

来源:中科芯MCU

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。