简 介

先楫半导体为客户提供了480MHz - 1GHz的不同主频高性能MCU,适用于不同高算力、实时控制要求的场合。在电机、电源应用场合,需要us级响应和运算,对响应时间的一致性、快速性都有非常高的要求。随着MCU主频提高,MCU的存储方式和总线频率也更加多样化,先楫MCU中内部有ILM、DLM、AXI_SRAM、flash等多种存储空间,但同时不同存储需要的时钟也不同,给软件工程师设计带来很大困扰。先楫在官网已经提供了优化DSP和FFT运算、使用片上SRAM等相关应用文档。

本文重点简述基于电机、电源应用的具体代码优化方案。

1、ILM程序优化

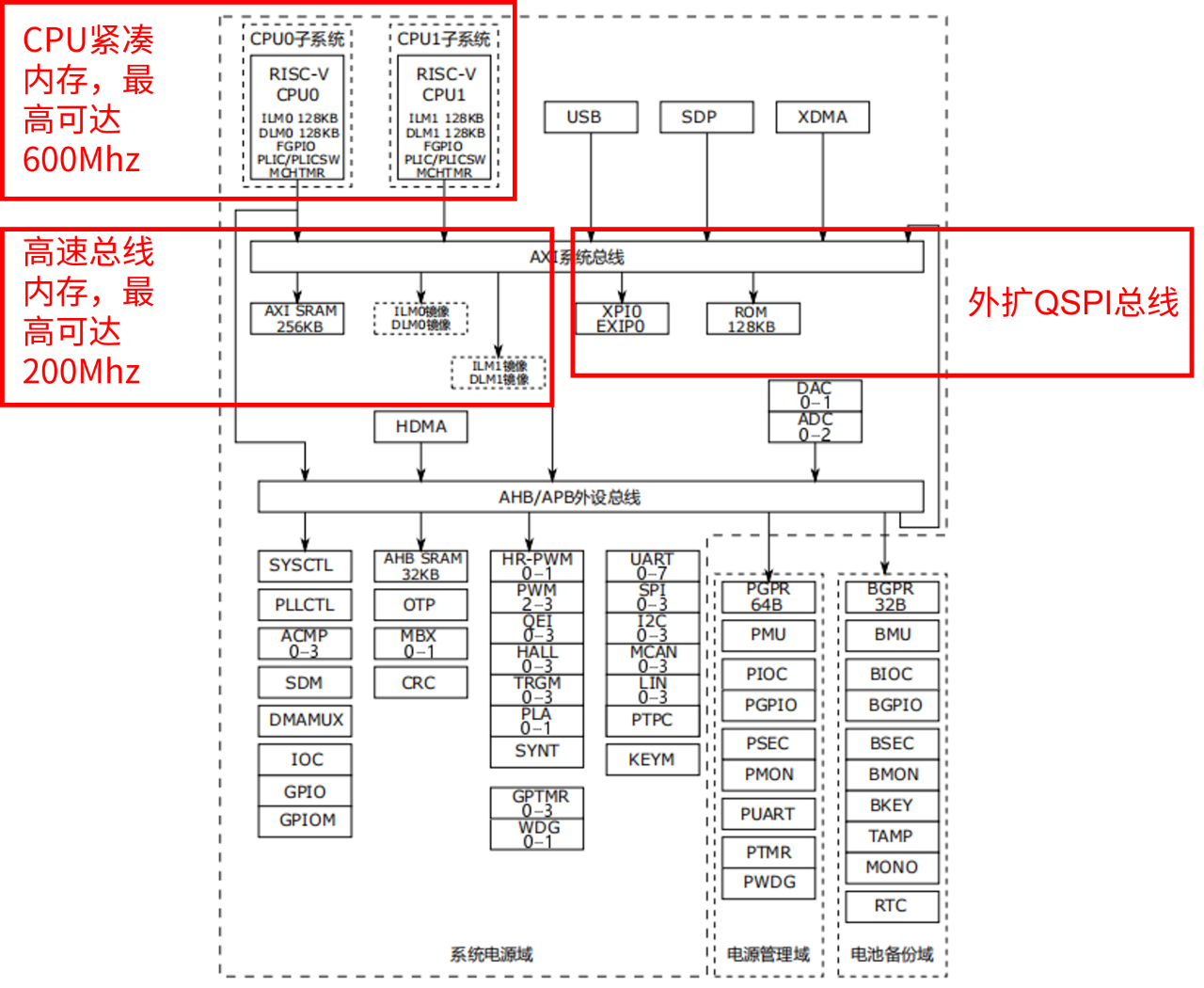

以下展示的是HPM6280的系统框图

CPU内部包含了ILM、DLM、cache,这些内存都可达 600Mhz主频。AXI总线上有AXI_SRAM和ILM_SLV、DLM_SLV,访问频率可达200MHz,总线宽度64bit,可以cache缓存。XPI接口为QSPI总线,最高频率133Mhz,双沿采样,通常只有4bit宽度。其中AHB总线还有32kbyte SRAM,但主要用于外设存储,这里不做赘述。

实际应用中程序都会放到flash中存储,而XPI的接口速度极大限制了代码执行效率。此外,由于XPI接口是可以cache缓存,导致XPI执行时cache命中和没有命中的运行时间差别非常大,代码一致性很差。为了方便客户使用,可以生成工程时选用debug/release模式,指定程序在ILM中执行。随后通过先楫manufacture tool可以实现镜像功能,即生成在从FLASH 加载的RAM启动镜像。通过这种方式实现代码完全在ILM中执行。

镜像助手可将SDK中的debug/release 构建的应用转化为FLASH启动镜像。

关键参数:

固件首地址相对容器首地址偏移

加载地址

入口点地址

2、SEGGER编译优化在AXI_RAM执行

由于ILM空间限制,很多电源或电机复杂应用无法将程序全部放到ILM中执行,会导致因读取存储速度限制了CPU算力。

HPM6200、HPM6E00系列在AXI总线的大容量SRAM可以配置成程序存储,其中HPM6260、HPM6E60还可以将CPU1的ILM、DLM配置到AXI总线上,基本满足了绝大部分应用。AXI RAM主频可达200Mhz,64bit位宽,有cache缓存,可以大大减少程序读取对CPU性能的影响。

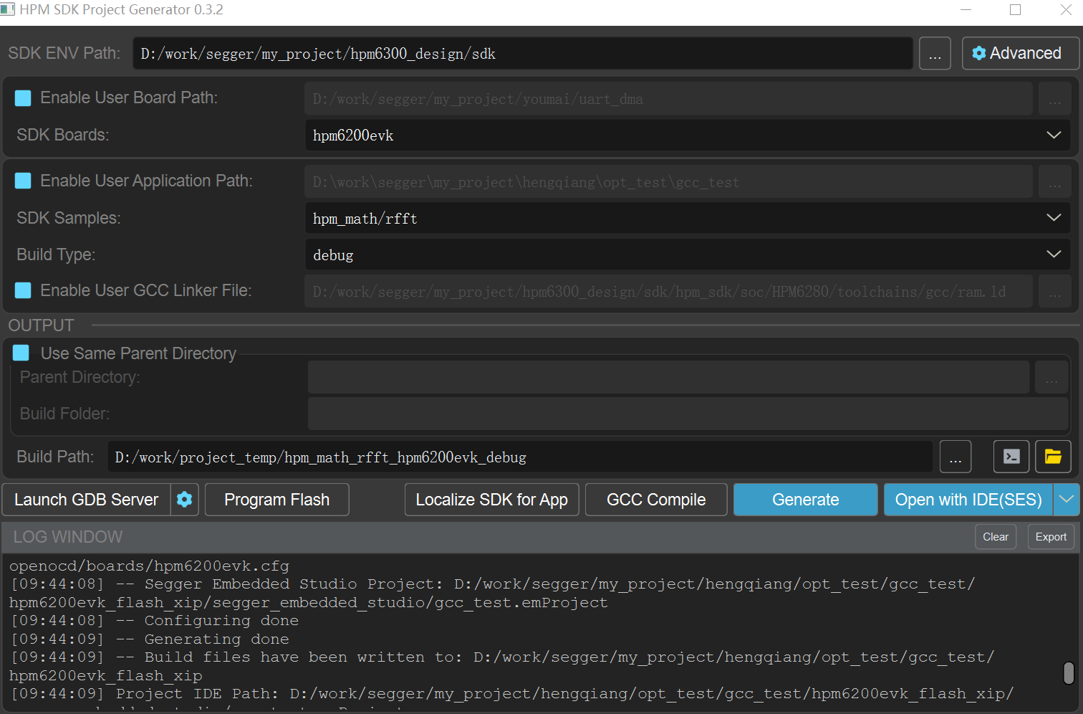

segger编译器可以自动生成flash加载到RAM的拷贝代码,只要在linker文件中配置相应特性,不需要额外修改flash拷贝代码。

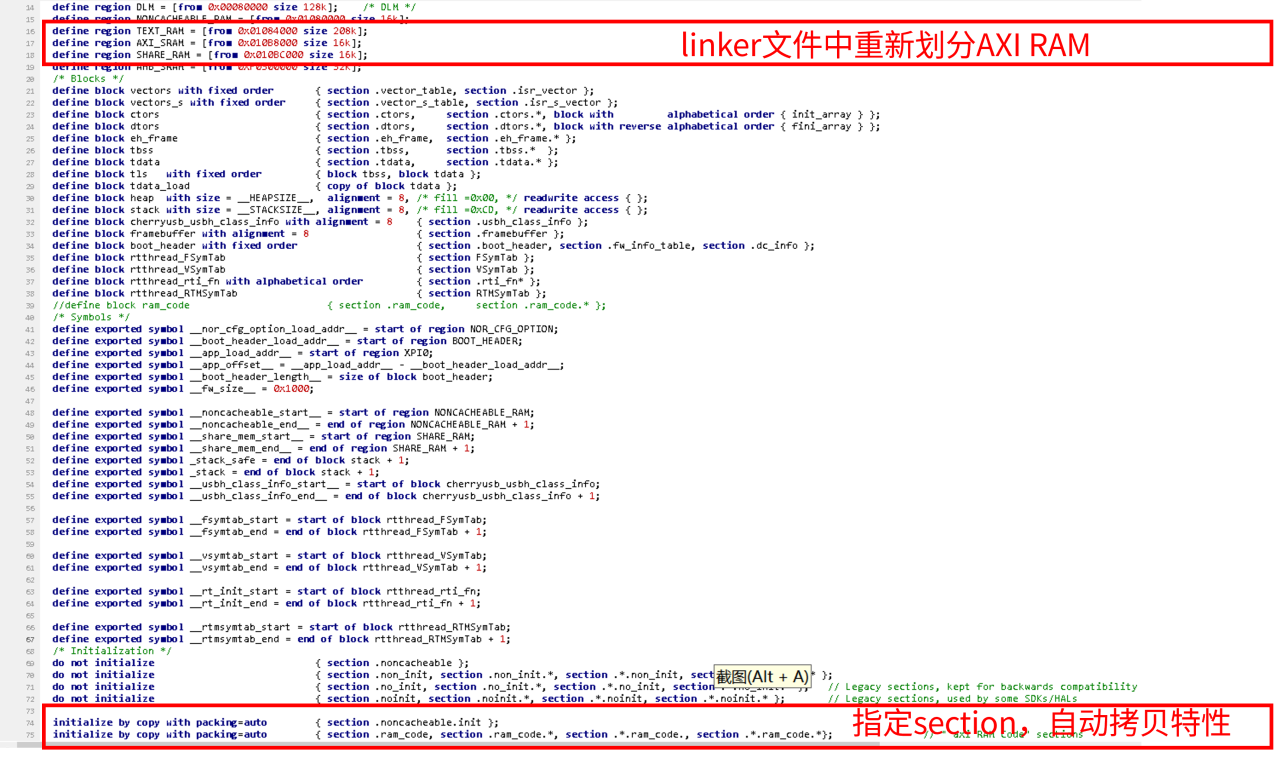

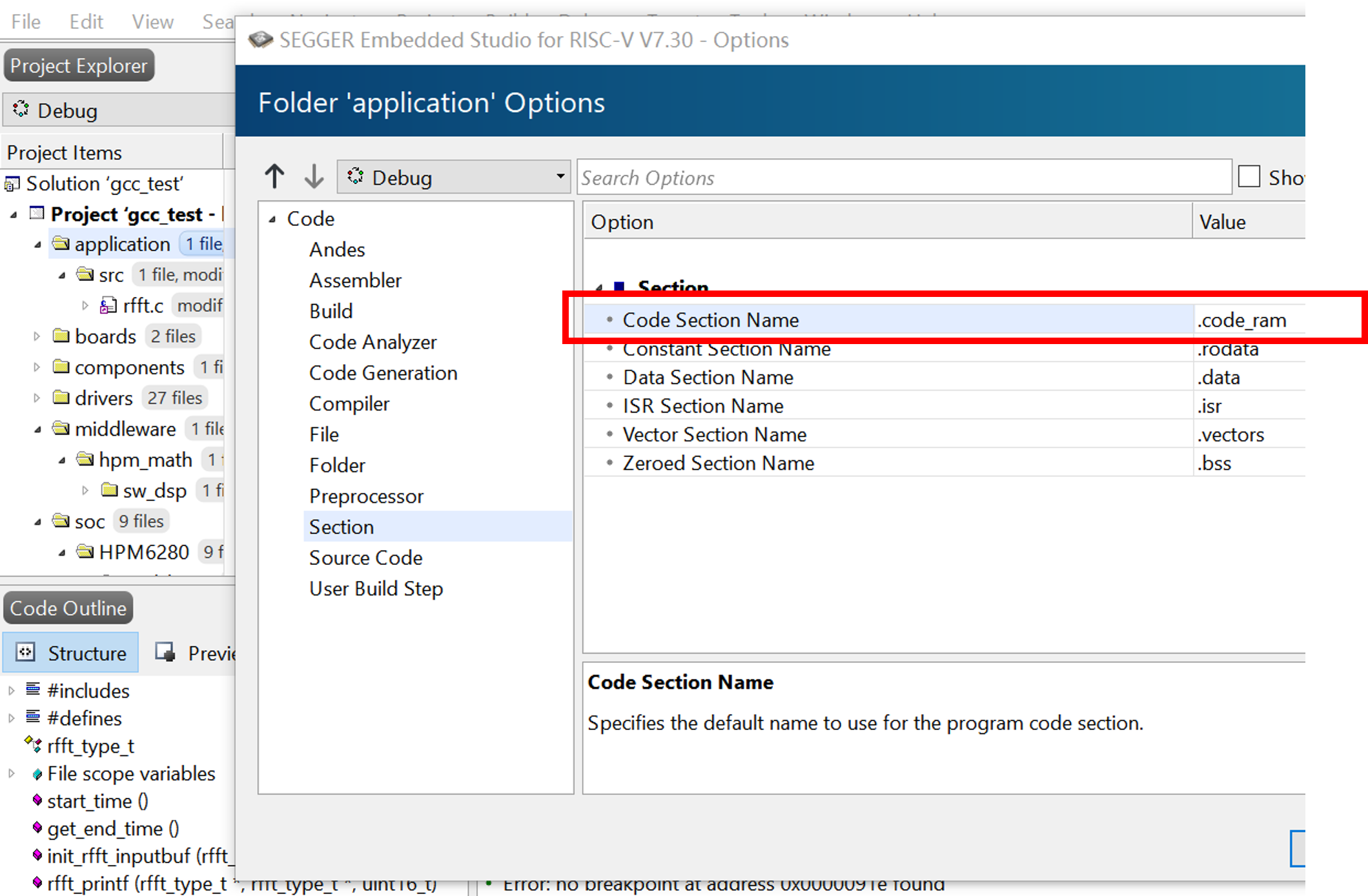

在linker文件中重新划分AXI RAM,增加代码区域。在软件中指定代码生成后存放区域。

通过SDK GUI直接指定修改后的linker文件,即可实现代码在ILM+AXI RAM中执行。

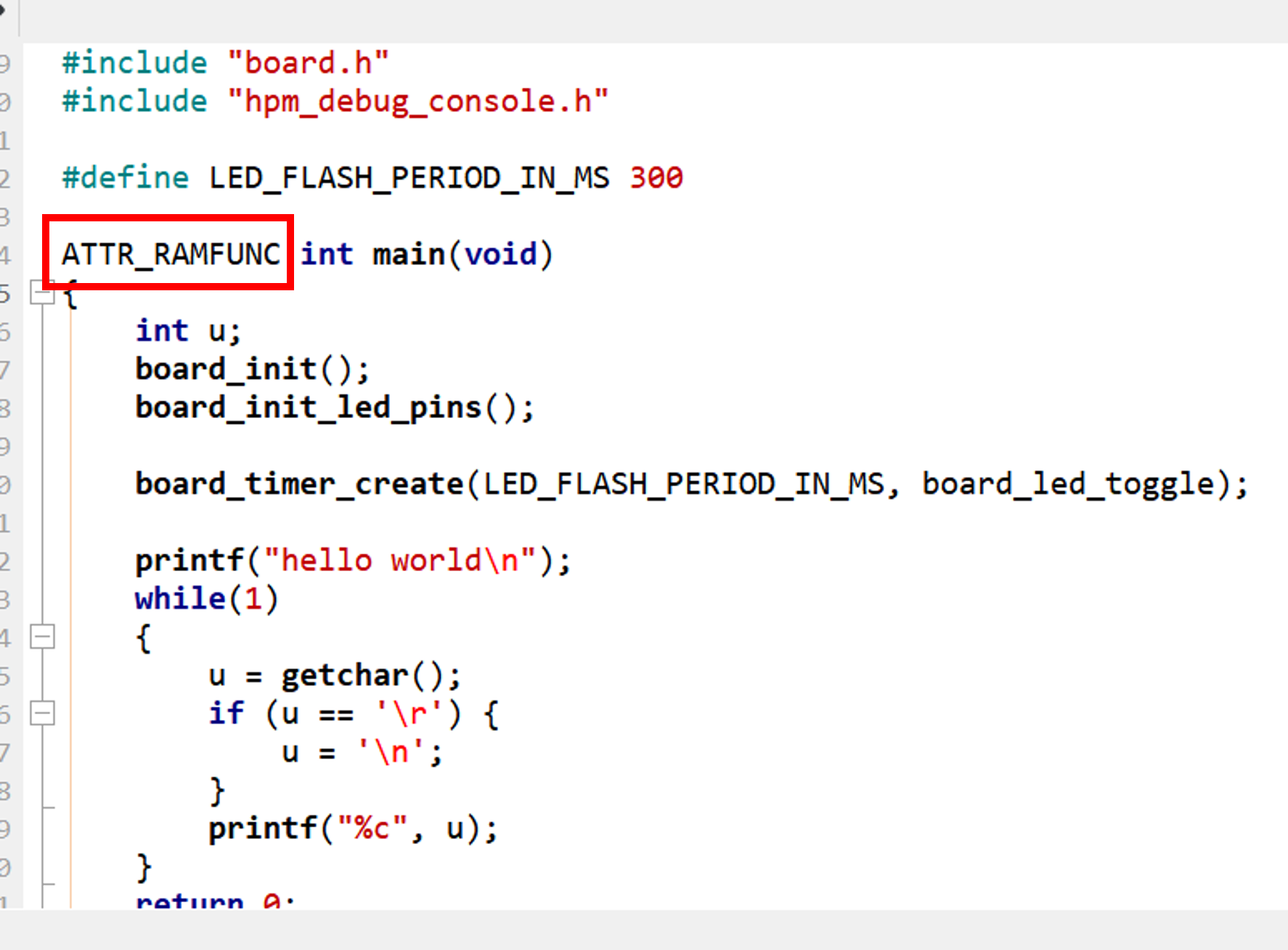

代码指定区域可以通过SEEGER IDE批量指定文件或文件夹的程序放置区域,也可以在函数名前面增加函数宏定义。

3、GCC编译优化在AXI_RAM执行

先楫产品支持Andes加速指令,可以加速三角函数、指数运算等复杂运行速度,但同时需要GCC编译器支持。

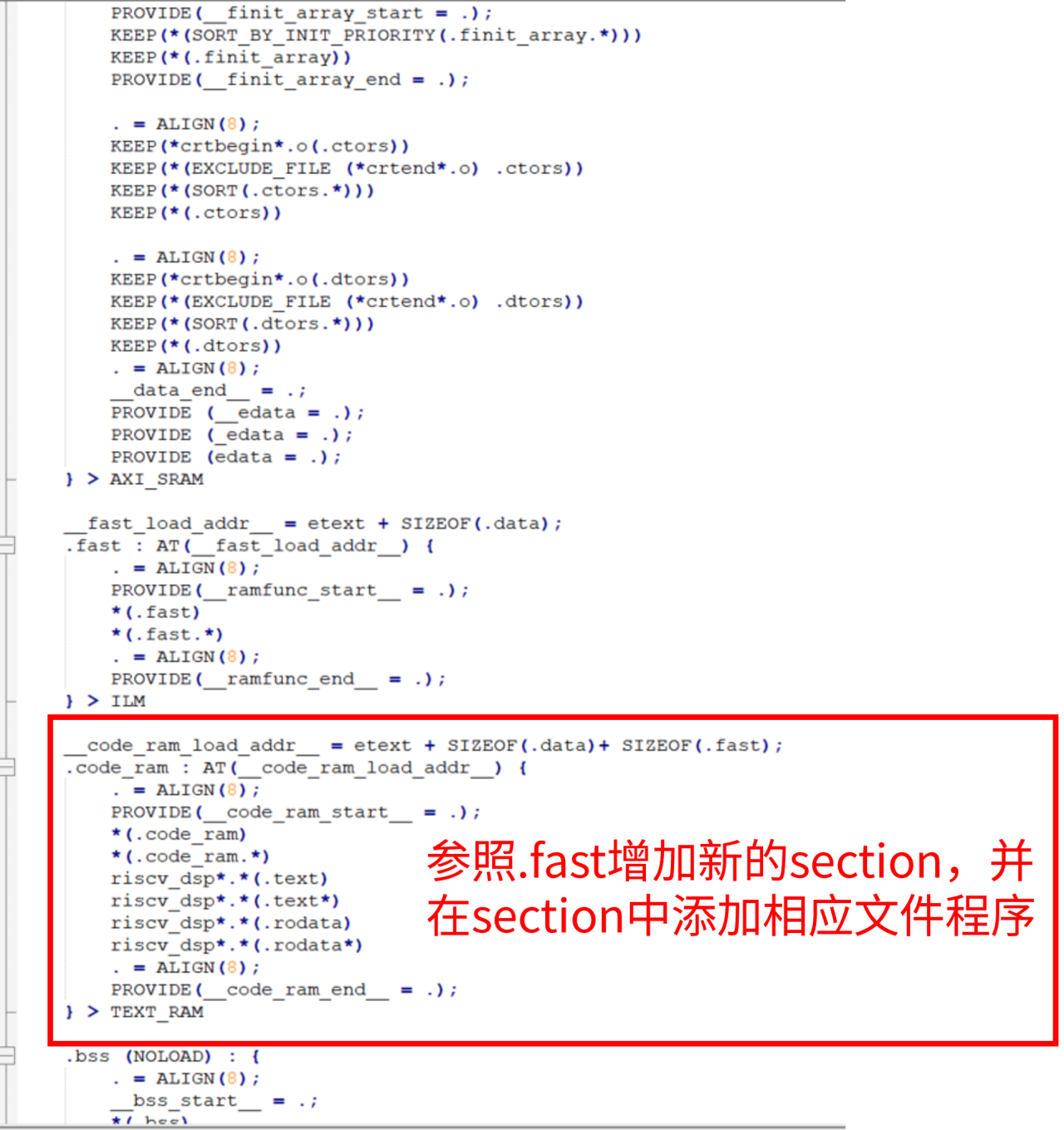

在linker文件中重新划分AXI RAM,增加代码区域。在软件中指定代码生成后存放区域。

与segger编译器不同,GCC编译需要增加额外代码实现flash加载到RAM的拷贝,需要修改相应的reset.c文件。

支持Andes加速指令需要引用hpm_math.h库文件,会调用libdspf.a、libdspd.a、libdsp.a等封装库。由于封装库非明文代码,无法通过常规方法指定代码存放区域,导致调用该代码时会因代码放置在flash降低整体执行速度。需要在linker文件中额外配置响应代码区域分配。

GCC编译后无法像segger一样编译后通过图形显示生成代码的占有率,且map文件阅读性差。对gcc编译的map文件需要引用AMAP.EXE工具。

GCC编译需要增加额外代码实现flash加载到RAM的拷贝,相应代码位于 SOC/HPM6XXX/TOOLCHAINS/GCC/reset.c 中。

在reset.c中函数c_startup实现flash到RAM程序的拷贝。

程序运行时,会以start.s开始,进入main函数之前先调用c_startup 函数完成程序搬移,在客户的应用代码中不会因程序放置位置不同而增加额外操作。

4、优化小知识

segger编译器会将所有常数默认为定点数,即使该常数为小数,也需要在对应常数前加强制浮点转换或者在常数后面加“f”做说明。

函数的inline定义在optimization level=0时是无效的,需要把优化等级设为1或更高。

建议将常用函数或变量通过attribute属性定义到“.fast”和“.fast_ram”。

先楫MCU为多总线系统,当CPU读写外设时会有时钟同步问题,建议在配置外设时尽量提高外设频率,减少时钟同步延迟。

HPM6260以及HPM6E60可以通过ILM_SLV、DLM_SLV接口可以将CPU1的内部存储作为AXI_RAM使用。

来源:先楫半导体HPMicro

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。