本期开发笔记由费神编写主要会为大家介绍HPM6000系列的各类片上SRAM并结合Segger Embedded Studio的linker文件介绍,提供了如何使用这些SRAM的建议,赶快来了解吧~

简介

在HPM6000系列微控制器上,集成了大容量的SRAM,可供用户存放代码,数据等,满足各类应用的需要。其中片上SRAM有多种分类,包括RISC-V CPU的指令和数据本地存储器ILM,DLM,通用内存AXI SRAM,AHB SRAM等,还包括AHB SRAM,APB SRAM等。这些SRAM的最高访问频率不同,数据保持的条件也不同,恰当地使用他们,可以极大的提升用户应用的效率。

片上SRAM介绍

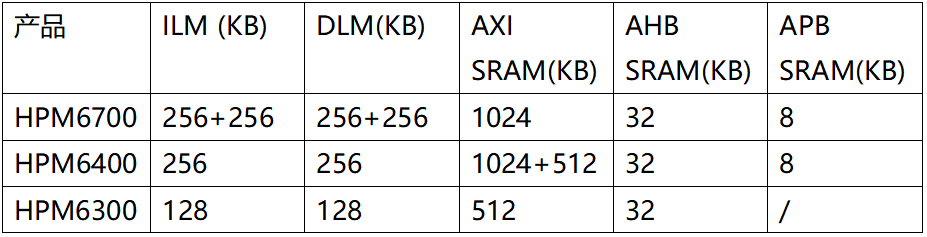

HPM6000系列高性能MCU均集成了大容量片上SRAM,总结如下:

HPM6000系列片上SRAM总结

HPM6000系列片上SRAM总结

2.1 RISC-V CPU的本地存储器ILM和DLM

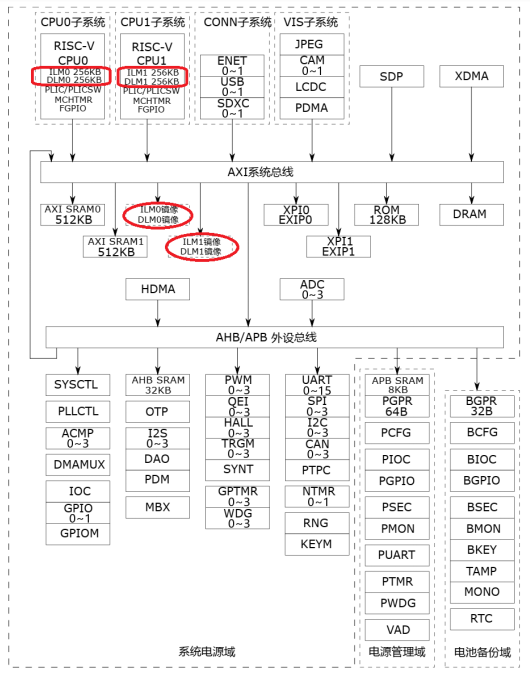

HPM6000系列高性能微控制器的RISC-V CPU都包含有指令和本地存储器,分别称为ILM(Instruction Local Memory,指令本地存储器)和DLM(Data Local Memory,数据本地存储器)。如下图所示,RISC-V CPU的ILM和DLM各自对应了内存映射表(Memory Map)中的2块地址映射区域。

HPM6700系列ILM/DLM示意图

ILM的映射有:

ILM,以HPM6700系列为例,容量256 KB,地址范围为0x00000000 ~ 0x0003FFFF。该地址区域只有RISC-V CPU可以通过自身的ILM接口访问,RISC-V CPU从ILM取指时,可以实现零等待周期,即ILM的访问时钟频率,与RISC-V CPU主频一致,并且RISC-V CPU的一级高速指令缓存I-Cache-L1对ILM无效。

CPUx_ILM_SLV,以HPM6700系列的CPU0 ILM为例,容量256 KB,地址范围为0x01000000 ~ 0x0103FFFF。该地址区域也称为ILM0镜像,该地址区域可以供总线上所有的主设备访问,如DMA等,包括RISC-V CPU自身,也可以通过CPUx_ILM_SLV访问ILM。如图所示,CPUx_ILM_SLV是AXI系统总线的从接口,其访问时钟频率与总线时钟频率一致。RISC-V CPU访问CPUx_ILM_SLV时,一级高速指令缓存I-Cache-L1是有效的。

DLM的映射有:

DLM,以HPM6700系列为例,容量256 KB,地址范围为0x00080000 ~ 0x000BFFFF。该地址区域只有RISC-V CPU可以通过自身的DLM接口访问,RISC-V CPU从DLM读写数据时,可以实现零等待周期,即DLM的访问时钟频率,与RISC-V CPU主频一致,并且RISC-V CPU的一级高速指令缓存D-Cache-L1对DLM无效。

CPUx_DLM_SLV,以HPM6700系列的CPU0 DLM为例,容量256 KB,地址范围为0x01040000 ~ 0x0107FFFF。该地址区域也称为ILM0镜像,该地址区域可以供总线上所有的主设备访问,如DMA等,包括RISC-V CPU自身,也可以通过CPUx_DLM_SLV访问ILM。如图所示,CPUx_DLM_SLV是AXI系统总线的从接口,其访问时钟频率于总线时钟频率一致。RISC-V CPU访问CPUx_DM_SLV时,一级高速指令缓存D-Cache-L1是有效的。

2.1.1 HPM6700系列

HPM6700系列微控制器上,指令/数据本地存储器的2块地址映射xLM和CPUx_xLM_SLV虽然地址不同,但访问的是同一块物理内存,RISC-V CPU可以通过xLM访问自身的指令/数据本地存储器,而其他总线主设备,比如DMA,需要通过CPUx_xLM_SLV来访问CPUx的指令/数据本地存储器。注意,RISC-V CPU本身,也可以通过CPUx_xLM_SLV访问自己的指令/数据本地存储器。

HPM6700系列支持双核RISC-V CPU,CPU从xLM地址映射总是访问到自身指令/数据本地存储器,而从CPUx_xLM_SLV可以访问到自身或者另一个CPU的指令/数据本地存储器。

以HPM6700系列RISC-V CPU0为例,从0x00000000和0x01000000读取到的,是CPU0指令本地存储器ILM0的首地址。从0x01180000读到的,是CPU1指令本地存储器ILM1的首地址。

以RISC-V CPU1为例,从0x00000000和0x01180000读取到的,是CPU1指令本地存储器ILM1的首地址。从0x01000000读到的,是CPU0指令本地存储器ILM0的首地址。

2.1.2 HPM6300系列

HPM6300系列为单核RISC-V CPU,RISC-V CPU和其他总线主设备都可以通过xLM地址映射访问CPU的指令/数据本地存储器,其中RISC-V CPU仍然可以通过自身的xLM接口对xLM实现零等待周期访问,即xLM的读写时钟频率与CPU的时钟同频。而其他总线主设备,需要以AXI系统总线的时钟频率访问xLM。

同时,xLM的镜像,CPUx_xLM_SLV映射仍然有效,包括RISC-V CPU在内的所有总线主设备,访问CPUx_xLM_SLV与访问xLM效果相同,访问的是同一块物理内存。注意RISC-V CPU通过CPUx_xLM_SLV访问自身的xLM时,会和其他总线主设备一样,读写时钟频率与AXI系统总线时钟频率一致,不再支持零周期等待,但是CPU的高速一级缓存会生效。

比如,RISC-V CPU和DMA,从0x00000000读取到的,是CPU0指令本地存储器ILM0的首地址。从0x01000000读取到的,也是CPU0指令本地存储器ILM0的首地址。注意RISC-V CPU从0x01000000取值后,如果高速缓存打开,其数据会被存入缓存。

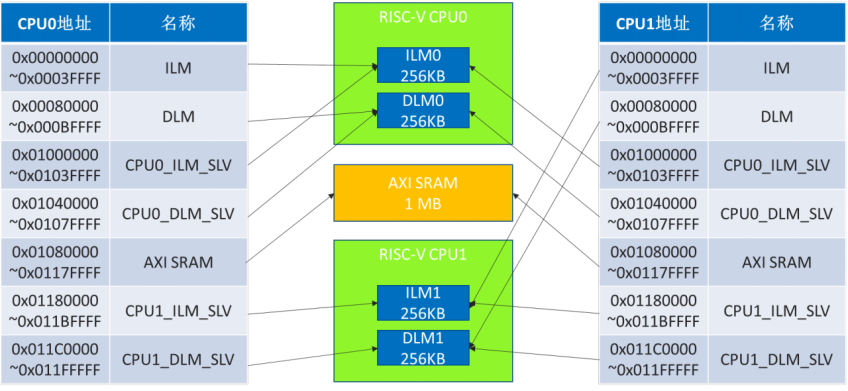

2.2 AXI总线SRAM

HPM6000系列高性能MCU支持通用的片上SRAM,称为AXI SRAM,可以用来存放数据或者代码。

HPM6700系列AXI SRAM示意图

上图以HPM6700系列MCU为例,展示了AXI SRAM在系统中的位置。顾名思义,AXI SRAM连接到AXI系统总线的从接口,它的读写时钟频率就是AXI系统总线的时钟频率。所有的AXI系统总线主设备都可以访问AXI SRAM。

注意:系统内存映射表上,AXI SRAM的地址映射与RISC-V CPU的ILM/DLM镜像映射CPUx_xLM_SLV在地址上是连续的。因此可以把AXI SRAM和RISC-V CPU的本地存储器当作一块联系的大内存使用。详情请参考后文的SRAM使用建议。

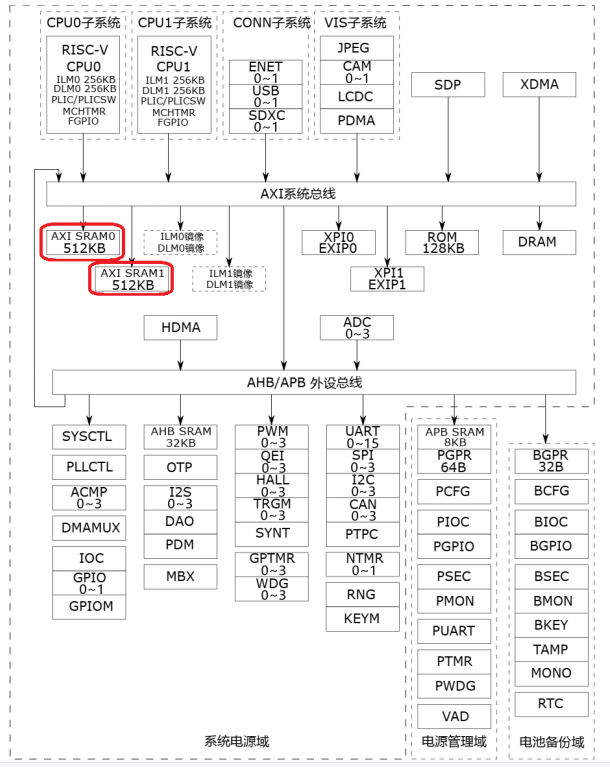

2.3 AHB总线SRAM

HPM6000系列高性能MCU包含挂载在外设总线AHB的片上SRAM,称为AHB SRAM,如下图所示,AHB SRAM连接到AHB外设总线的从设备接口。

AHB SRAM的读写时钟频率为AHB外设总线的时钟频率。注意,包括RISC-V CPU在内的总线主设备需要通过AXI系统总线,来访问AHB外设总线下的各个外设寄存器。而外设总线AHB上的主设备,比如HDMA,可以直接通过AHB总线访问外设寄存器,以及AHB SRAM。因此AHB SRAM比其他类型的片上SRAM更适合用作寄存器和SRAM之间的数据搬运。基于同样的理由,HDMA也比XDMA更适合用作AHB SRAM和寄存器之间的数据搬运。

因此,当使用HDMA用作通讯接口,如UART,SPI的数据收发时,推荐使用AHB SRAM作为数据的缓冲区。

HPM6700系列AHB SRAM和APB SRAM示意图

2.4 APB总线SRAM

HPM6000系列高性能MCU的部分型号支持APB SRAM。上图以HPM6700系列MCU为例,展示了APB SRAM在系统中的位置。

APB SRAM位于电源管理域,由VPMC引脚供电。当MCU处于低功耗模式时,有可能通过关闭系统电源域的电源,使得VDD_SOC掉电。此时,APB SRAM可以作为片上的备份SRAM,保存必要的数据。

注意,对于不支持APB SRAM的型号,可以使用电源管理域通用寄存器PGPR,保存一定的备份数据。

在电池模式(VBAT Only Mode)下,VPMC也掉电,HPM6000系列MCU仅VBAT保持供电。此时,电池备份域通用寄存器BGPR,可以用来保存一定的备份数据。

以上为本期分享内容,还有更多信息如 Segger Embedded Studio的linker文件说明,以及SRAM的使用说明和相应的linker文件修改方法,可点击文链接:https://www.hpmicro.com/resources/resources.html进行了解,感谢关注!

来源:先楫芯上人

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。