概念基础:

STM32时钟系统基本一致,不同系列之间有细微差别。此文档主要针对STM32F446的时钟系统进行介绍。

1. 时钟树概述

① 为何不是采用一个系统时钟?如51

因为STM32本身非常复杂,外设非常多,但是并非所有外设都需要系统时钟这么高的频率,比如看门狗和RTC只需要几十K的时钟即可。同一个电路,时钟越快,功耗越大,同时抗电磁干扰能力也会越弱,所以对于较为复杂的MCU一般采用多时钟源的方法来解决这些问题。

② 主要时钟源:

5个最主要的时钟源:

高速时钟源:HSI、HSE、PLL

低速时钟源:LSI、LSE

其中PLL实际又分为3个时钟源:主PLL、I2S部分专用PLLI2S、SAI部分专用PLLASI。

详解:

LSI是低速内部时钟,RC振荡器,频率为32K,供独立看门狗和自动唤醒单元使用。

LSE是低速外部时钟,接频率为32.768Khz的石英晶体,这个主要是RTC的时钟源。

HSE是高速外部时钟,频率范围为4Mhz-26Mhz,可以直接作为系统时钟或PLL输入。

HSI是高速内部时钟,RC振荡器,频率为16Mhz,可以直接作为系统时钟或PLL输入。

PLL为锁相环倍频输出,STM32F4有三个PLL:

a、 主PLL由HSE或HSI提供时钟信号,并具有两个不同的输出时钟。

第一个输出PLLP用于生成高速的系统时钟(最高180Mhz)

第二个输出PLLQ为48M,用于USB OTG FS时钟,随机数发生器的时钟和SDIO时钟。

b、 第一个专用PLL(PLLSAI)用于生成精确时钟,用作SAI输入时钟。Q是SAI时钟分频系数。P可以生成PLL48CLK用于给USB FS或SDIO提供48M时钟。

c、 第二个专用PLL(PLLI2S)用于生成精准时钟,在I2S和SAI上实现高品质音频性能。R是I2S时钟的分频系数,Q是SAI时钟的分频系数。

2. 常用时钟源选择

① 看门狗时钟:看门狗时钟只能是低速的LSI时钟,32Khz。

② RTC时钟源:可以选择LSI(32Khz)、LSE(32.768Khz)、HSE分频后提供(2-31分频)

③ 系统时钟SYSCLK:可选择HSE、HSI和PLL

④ USB高速设备会有外部PHY提供60Mhz

⑤ NOTE:

在上述的很多时钟输出中,有很多是带使能控制的,例如AHB总线时钟、内核时钟、各种APB1外设、APB2外设等。

APB1是外设低速总线

APB2是外设高速总线

一般时钟总线是设备总线的2倍

时钟主频可以设置为168Mhz,通过设置Over-driver模式可以超频到180Mhz

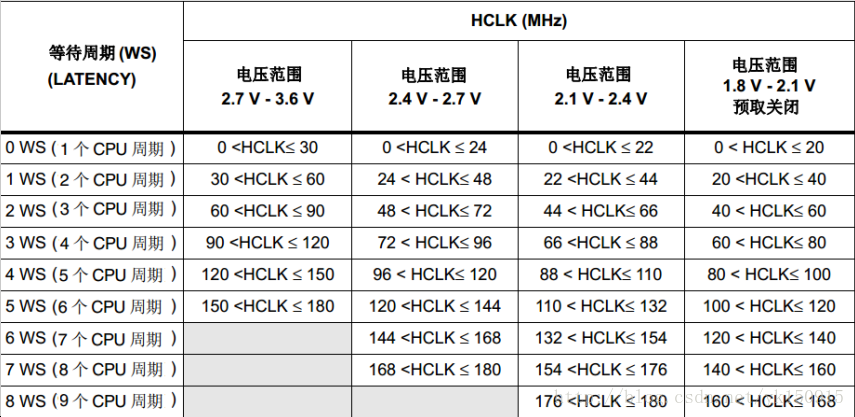

FLASH Latency 延时配置参考:

3. 时钟源使能和配置

在配置好时钟系统之后,如果我们要使用某些外设,例如GPIO、ADC,还要使能这些外设时钟,如果在使用外设之前没有使能外设时钟,这个外设是不可能正常运行的。

IO引脚复用器和映射

一个GPIO如果可以复用为内置外设的功能引脚,那么这个GOIO作为内置外设使用的时候,就叫做复用。

4. 寄存器配置

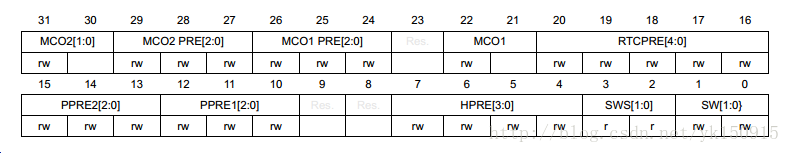

① RCC_CFGR,时钟配置寄存器

Bit2 bit3代表使用的时钟源,具体可查参考手册,系统刚上电时默认为内部HSI。

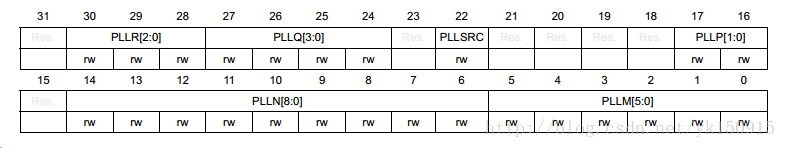

② RCC_PLLCFGR,PLL时钟配置寄存器

上电默认情况为HSI做为主PLL和I2SPLL的时钟入口。

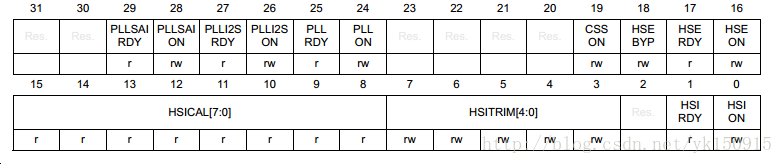

③ RCC_CR,RCC时钟控制寄存器

通过Bit16可以切换为外部晶振。在时钟初始化的时候被调用。时钟切换之后,根据时钟设置逻辑,如果外部晶振使能了,则等待外部晶振正常起震。起震后查看RCC_CFRG寄存器,当前使用的还是HSI。下一步需要判断程序中是否要使用PLL,若使用,则继续进行PLL配置。

配置结束PLL的各种分频后,一块进行寄存器配置。此时再切换到外部HSE工作。

时钟配置过程:

(1)AHB配置预分频,得到HCLK时钟,分频值写入RCC_CFGR bit4-bit7

(2)系统时钟配置 RCC_CFGR bit0-bit1

(3)检查系统时钟状态是否切换成功 RCC_CFGR bit2-bit3

(4)APB1、APB2配置预分频,得到PCLK1、PCLK2时钟RCC_CFGR bit10-bit15

(5)更新系统全局变量SystemCoreClock

5. I2S时钟配置

(1)选择I2S外设的时钟源

(2)配置各项时钟分频系数,一般情况下使用PLLI2SR时钟

(3)计算时钟分频,需要在PLLI2SR上获得需要的48K

下列公式为参考手册提供:

When the master clock is generated (MCKOE in the SPIx_I2SPR register is set):

fS = I2SxCLK / [(16*2)*((2*I2SDIV)+ODD)*8)] when the channel frame is 16-bit wide

fS = I2SxCLK / [(32*2)*((2*I2SDIV)+ODD)*4)] when the channel frame is 32-bit wide

When the master clock is disabled (MCKOE bit cleared):

fS = I2SxCLK / [(16*2)*((2*I2SDIV)+ODD))] when the channel frame is 16-bit wide

fS = I2SxCLK / [(32*2)*((2*I2SDIV)+ODD))] when the channel frame is 32-bit wide

将计算额I2SDIV和奇数值ODD写入相应寄存器。

此例中,I2SxCLK为192MHz,使用48K时可以被整除,时钟准确,但是96K时不能被整除,造成时钟偏移。所以若需要进行I2S时钟动态调节,需要好好计算I2SxCLK。

版权声明:本文为CSDN博主「yk150915」的原创文章,

遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/yk150915/article/details/79112766