RA2快速设计指南 [7] 模块停止功能,中断控制单元与低功耗

为了尽可能提高电源效率,RA2系列MCU允许通过对模块停止控制寄存器(MSTPCRi,i = A、B、C、D)执行写入操作来分别停止片上外设。模块停止后,将无法访问模块寄存器。

为了尽可能提高电源效率,RA2系列MCU允许通过对模块停止控制寄存器(MSTPCRi,i = A、B、C、D)执行写入操作来分别停止片上外设。模块停止后,将无法访问模块寄存器。

USART的功能包括同步、异步模式、双工通信、半工通信等。

单片机CPU在处理某一事件A时,发生了另一事件B请求CPU迅速去处理(中断发生);CPU暂时中断当前的工作,转去处理事件B(中断响应和中断服务);待CPU将事件B处理完毕后,再回到原来事件A被中断的地方继续处理事件A(中断返回),这一过程称为中断。

Cortex-M3内核支持256个中断,其中包含了16个内核中断(异常)和240个外部中断,并且具有256级的可编程中断设置。但是,STM32并没有使用CM3内核的全部东西,而是只用了它的一部分。

中断响应与返回:CPU采集到中断请求信号,怎样转向特定的中断服务子程序,并在执行完之后返回被中断程序继续执行。期间涉及到CPU响应中断的条件,现场保护,现场恢复。

概述

从本质上来讲,中断是一种电信号,当设备有某种事件发生时,它就会产生中断,通过总线把电信号发送给中断控制器。

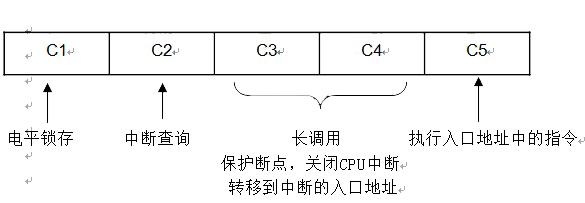

中断响应时间:从外部中断请求有效(外部中断请求标志置1)到转向中断入口地址所需要的响应时间。每个机器周期的S5P2时刻,INTx引脚的电平被锁存到内部寄存器中,待下一个周期查询。

1. 最短时间:中断请求有效,查询后在下一个周期便开始执行一条硬件的子程序的调用(时间是两个周期),然后开始执行服务程序的第一条指令。这样从锁存电平的周期到执行中断服务程序,中间相隔3个机器周期。

2. 最长时间:如果中断信号发生在前面所说的3种情况时,响应时间就要变长:

(1)响应时间取决于正在执行的同级或高级中断的执行时间;

(2)指当前CPU执行的指令是多周期指令,如乘除法指令(4个周期),最坏情况,还要等3个周期。这样响应周期变为3+3=6个周期;

(3)CPU当前执行的指令是RETI或访问IE、IP寄存器时,本指令(1个周期)没有响应,且下一条指令执行完后才能响应,这样附加的等待时间最长不会超过5个周期(1+4)。整个响应为5+3=8个周期。

1、简述

下面这张图是一条外部中断线或外部事件线的示意图。图中的蓝色虚线箭头,标出了外部中断信号的传输路径;图中红色虚线箭头,标出了外部事件信号的传输路径。

MCS-51中断系统:5个中断源(两个外部中断, 两个定时器, 一个串口),2个优先级