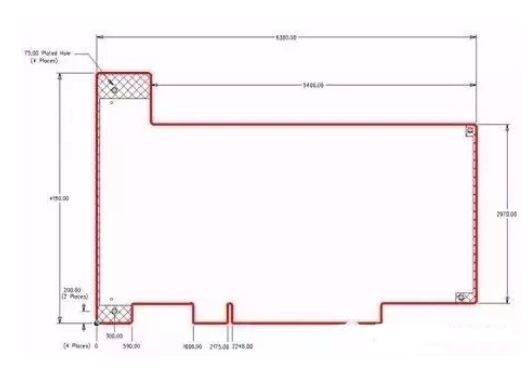

2.1.印制电路板

印制电路板(Printed Circuit Board,简称PCB)在电子设备中是电子元器件的载体,提供机械支撑和电气连接,并保证电子产品的电气、热和机械性能的可靠性。为自动焊锡提供阻焊图形,为电子元器件安装、检查、维修提供识别字符和图形。

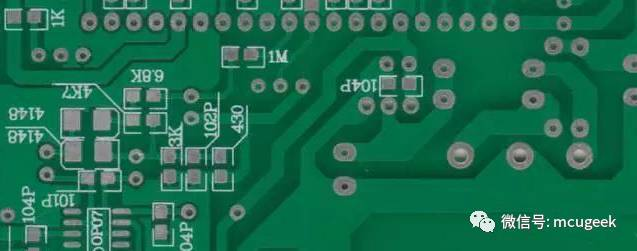

PCB板由焊盘、导线、丝印、绝缘漆、定位孔、导通孔、贯穿孔等要素构成:

(1)焊盘:焊盘是电路板上用来焊接元器件或引线的铜箔,经过回焊炉将锡膏熔解或过波峰焊后对零件进行固定;

(2)导线:用于连接电路板上各种元件的引脚,完成各个元件之间电信号的连接;

(3)丝印:也即白油,文字印刷标明零件的名称、位置、方向。PCB上有产品型号、版本、厂商标志和生产批号等;

(4)绝缘漆:绝缘漆作用是绝缘、阻焊、防止PCB板面被污染,黄油和绿油偏多;

(5)导通孔:PCB上充满或涂上金属的小洞,它可以与两面的导线相连接,又称VIA孔;

(6)贯通孔:用于插装通孔元器件;

(7)定位孔:用于将PCB固定在电子设备中。

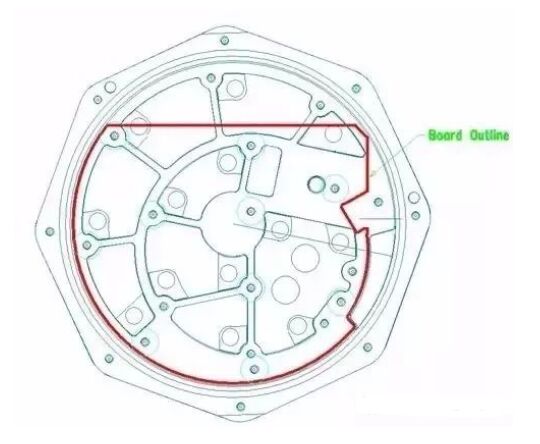

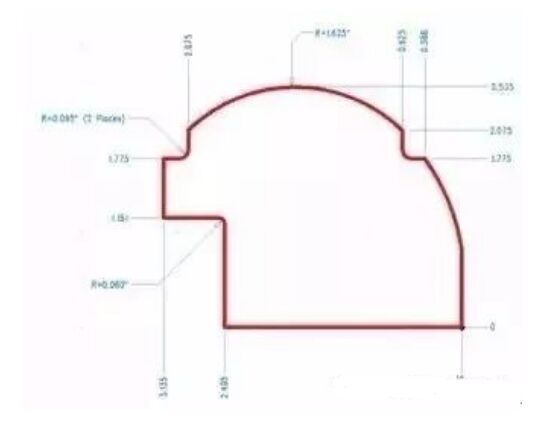

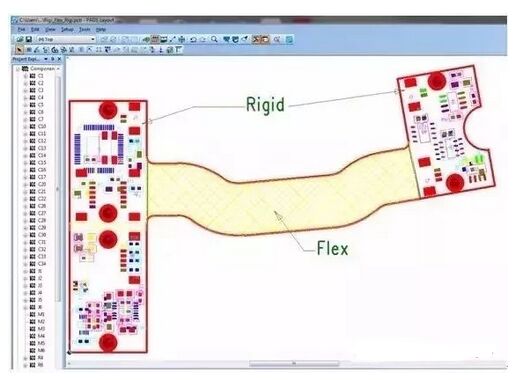

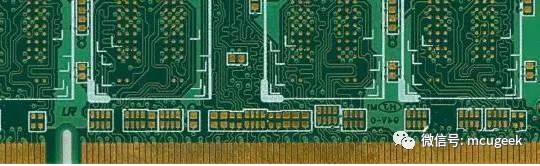

2.2 PCB的分类

PCB按印刷版电路层数可分为单面板、双面板、多层板;按基板材质分有刚性PCB、柔性PCB(挠性板)、刚柔结合PCB(刚挠结合板)等。与此同时,印制板继续朝着高精度、高密度和高可靠性方向发展,体积不断缩小,、成本不断减轻,而性能却不断提高,使得印制板在未来电子设备地生产过程中,仍然保持着强大的生命力。

2.3 PCB的基板材料

覆铜板(Copper Clad Laminates,简称 CCL)是PCB的基材,它是用增强材料,浸以树脂胶黏剂,通过烘干、裁剪、叠合成坯料,然后覆上铜箔,用钢板作为模具,在热压机中经高温高压成形加工而制成的。一般用来制作多层板的半固化片,是覆铜板在制作过程中的半成品,多为玻璃布浸以树脂,经干燥加工而成。

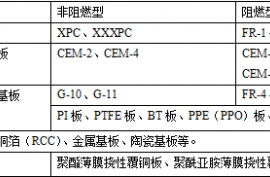

PCB基板材料,可分为纸基、玻璃布基、复合材料基(Composite Epoxy Material,简称CEM)、特殊材料基(陶瓷、金属芯基等)四大类,如表2-1所示。

按基板所采用的树脂胶黏剂不同进行分类,常见的纸基CCL有:酚醛树脂(XPc、XxxPC、FR-1、FR-2等)、环氧树脂(FR-3)、聚酯树脂等各种类型。常见的玻璃纤维布基CCL有环氧树脂(FR24、FR-5),它是目前使用最广泛的玻璃纤维布基类型。另外, 还有其他特殊性树脂,如双马来酰亚胺改性三嗪树脂(BT)、聚酰亚胺树脂(PI)、二亚苯基醚树脂(PPO)、马来酸酐亚胺—苯乙烯树脂(MS)、聚氰酸酯树脂、聚烯烃树脂等。

表2-1 PCB基材的分类

2.4贴片元器件(SMC/SMD)

2.4.1 SMC/SMD的封装

封装(Package)就是指把硅片上的电路管脚,用导线接引到外部接头处,以便与其它器件连接。封装形式是指安装半导体集成电路芯片用的外壳,它不仅起着安装、固定、密封、保护芯片及增强电热性能等方面的作用,而且还通过芯片上的接点用导线连接到封装外壳的引脚上,这些引脚又通过印刷电路板上的导线与其它器件相连接,从而实现内部芯片与外部电路的连接。

1.标准封装

(1)无源片式元件(CHIP)

长方形无源器件称为“CHIP”片式元器件,它的体积小、重量轻、抗冲击性和抗震性好、寄生损耗小,被广泛应用于各类电子产品中。主要用于电阻、电容、电感等元件,主要特点是没有突出的引脚。

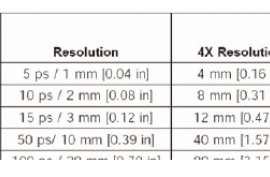

无源片式元件用两种尺寸代码来表示。一种尺寸代码是由4位数字表示的EIA(美国电子工业协会)代码,前两位与后两位分别表示电阻的长与宽,以英寸为单位。我们常说的0603封装就是指英制代码。另一种是米制代码,也由4位数字表示,其单位为毫米。英制的1005,0201、0402、0603、0805、1206片状元件,相当于公制的0402、0603、1005、1608、2012、3216(mm)元件,通常使用的都是英制标注,下表列出贴片电阻封装英制和公制的关系及详细的尺。

(2)柱状封装元件(MELF)

主要用于二极管、电阻、电感、陶瓷或钽电容等。焊接端头为圆柱体金属成份,如银、金或钯银合金等,易滚动,如图2-10。

图2-10 柱状元件

图2-10 柱状元件

(3)小外形晶体管(SOT,Small Outline Transistor )

主要用于二极管、三极管、达林顿管等。引出端特点是分列于元器件对称的两端,引脚为“一”和“L”形,基本分为对称与不对称两类,有以下几个系列SOT23、SOT89、SOT223等。

(4)小外形封装(SOP, Small Outline Package)

SOP封装主要用于中小规模集成电路。引出端特点是对称分列于元器件的两边,引脚形态基本分为“L”与“鸥翼”(Gullwing)、“J”、“I”等四类,如图2-12。SOP封装技术由1968~1969年菲利浦公司开发成功,以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等。

(5)四周扁平封装(QFP)

多用于各类型的集成电路,引脚形态基本上分为“鸥翼”形,引脚间距从0.3mm至1.0mm多个系列,封体形态为正方形或长方形,封装材料为塑料(PQFP)或陶瓷(CQFP)。

(6)塑封引线芯片载体(PLCC)

PLCC多用于各类型的集成电路,引脚形态为 “J”形,引脚间距1.27mm,封体形态为正方形或长方形、不规则形状,封装材料为塑料,可直接装入芯片插座或焊接。

(7)球栅阵列封装(BGA)

大规模集成电路的BGA封装发展缘由:集成电路的集成度迅速提高,封装尺寸必须缩小。电极采用球形引脚,球形引脚优点:尺寸小利于高密度组装;再流焊时有自校准效应,降低了贴片精度,提高组装可靠性。该类型封装已很多见,多用于大规模、高集成度器件,封装材料为塑料或陶瓷、金属,焊球间距为1.27mm、1.00mm、0.8mm、0.65mm、0.5mm等,球径随着间距而相应缩小,阵列规格多样,各家标准不一。BGA品种: 陶瓷BGA(CBGA)、塑料BGA(PBGA)、 微型BGA(Micro-BGA、μBGA、CSP)

(8)芯片尺寸封装(CSP)

该类型从形式上类似于BGA,但其定义为封装尺寸不大于芯片尺寸的1/3。有些公司的产品又称为μBGA。焊球间距一般均在1.00mm以下。

(9)倒装芯片(FP)

为目前最为先进的IC形式,应用晶圆片半导体工艺,产生具有规则或不规则凸点阵列,凸点间距在0.8mm以下,凸点直径在0.5mm以下,基本属裸芯片。

2.4.2SMC/SMD的包装

表面贴装元器件的大量应用,是由表面贴装设备高速发展促成的,同时高速度、高密度、自动化的贴装要求,又促使了表面贴装元器包装技术的开发,表面贴装元器件的包装形式已经成为SMT系统中的重要环节,表面组装元器件的包装类型有编带、管装、托盘等。

1.编带包装

编带包装在SMA生产中占有较大比例,常见的有电阻、电容以及各种IC等。带状包装由带盘与编带组成,类似电影拷贝

根据材质不同,有纸编带,塑料编带及黏结式编带,其中纸编带包装与塑料编带的元件,可用同一种带状供料器,而黏结式塑料编带所使用的带状供料器的形式有所不同,但不管哪种材料的包装带,均有相同的结构。

纸编带由基带、底带和带盖组成,其中基带是纸,而底带和盖带则是塑料薄膜。基带上布有小圆孔,又称同步孔,是供带状送料器上棘轮传动时的定位孔,两孔之间的距离称为步距。矩形孔是装载元器件的料糟,用来装载不同尺寸的元件。W指带宽,带宽已有标准化尺寸,有8mm,12mm,16mm,24mm和32mm等。用来装载0603以上尺寸元件的同步孔距均为4mm,而小于0603尺寸的包装带上的同步孔距则为2mm,故定购供料器时应加以区别。

2.管装包装

主要用于SOP、SOJ、PLCC、PLCC插座,以及异形元件等。

3.托盘包装

盘装又称华夫盘包装,它主要用于QFP、SOP等元件。通常这类元件引脚精细,极易碰伤,故采用上下托盘将元件的本体夹紧,并保证左右不能移动,便于运输和贴装。

2.4.3 SMC/SMD的储存与使用

1.存放环境条件:

(1)环境温度:30℃下;

(2)环境湿度:< 60%RH ;

(3)环境气氛:库房及环境中不得有影响焊接性能的疏、氯、酸等有害气体;

(4)防静电措施:要满足表面组装对防静电的要求。

2.存放周期:

从生产日期起为二年。到用户手中算起一般为一年(南方潮湿环境下3个月以内)。

3. 防潮

塑封元器件均对湿度有不同的敏感度,因而对敏感程度较高的元器件在包装中,除正常的产品标识、合格证外,正规厂家均会在其包装中放置若干物品,如:干燥剂、防潮袋、警示标签、湿度指标卡等,对具有防潮要求的SMD元件,打开封装后一周内或72小时内(根据不同元件的要求而定)必须使用完毕,如果72小时内不能使用完毕,应存放在< 20%RH的干燥箱内,对已经受潮的SMD器件按照规定作去潮烘烤处理。

4.防静电

操作人员在拿取SMD元件时应带好防静电手环、防静电手套等工具。

2.4.4 BOM的识读

物料清单(Bill of materail,简称 BOM)在电子组装生产中是一种非常重要的文件,是电子产品研发的成果性文件,也是电子企业中各个部门沟通的重要媒介,如采购部门根据BOM可以知道要采购哪些元器件,生产部门根据BOM清楚的知道,线路板的组装过程中每个元器件数量以及安装位置。要清楚生产用料必须学会看BOM,如表2-21所示,阅读BOM主要注意几方面:

1. 要清楚产品型号、版本,如VA-391 V3.2

2. 区分BOM中哪些是SMC/SMD,哪些是THC:

BOM描述中有下列文字或字母之一都是SMT用料 “SMD、0603、0805、1206、Chip、SMT、QFP、PLCC、BGA、SOJ”;

插装件一般有“DIP”字样,但电解电容一般为DIP型,BOM上通常省去“DIP”字样,如:BOM 第31行对电解电容的描述为6.8uF/400V,Φ8*15,105℃,20%。

3.有些零件要看外形才知属SMD还是DIP元件。举例:

(1)描述为chip CAP 0.01μF 50V +80%-20% SMD 0603

表示:该电容是晶片陶瓷电容,容值为0.01μF ,耐压50V,误差为+80%-20%,即容值允许范围: 0.018μF ~0.008μF ,SMD 0603型的;

(2)描述为chip Resister 10 OHM 1/10W 5% 0603

表示:该晶片电阻阻值为10Ω,功率为0.1瓦,误差为±5% 0603规格;

(3)描述为:Chipset Sis6326 H0 208-Pin PQFP

表示:该芯片为SIS公司名称为6326版本为H0,208个脚,PQFP型;

(4)描述为:PCB VA-391 V3.2 16×8.3cm,4-L SS Yellow

表示:该PCB为VA-391,版本为3.2,长×宽×厚为143*112.5*1.6MM,基板材料为,FR-4的双面板。

4.看清楚描述是否有指定零件的厂牌及颜色等。

5.位置是指零件用在PCB板上的位置以及数量。

表2-21 VA-391 V3.2 主板BOM

来源: 电子技术应用