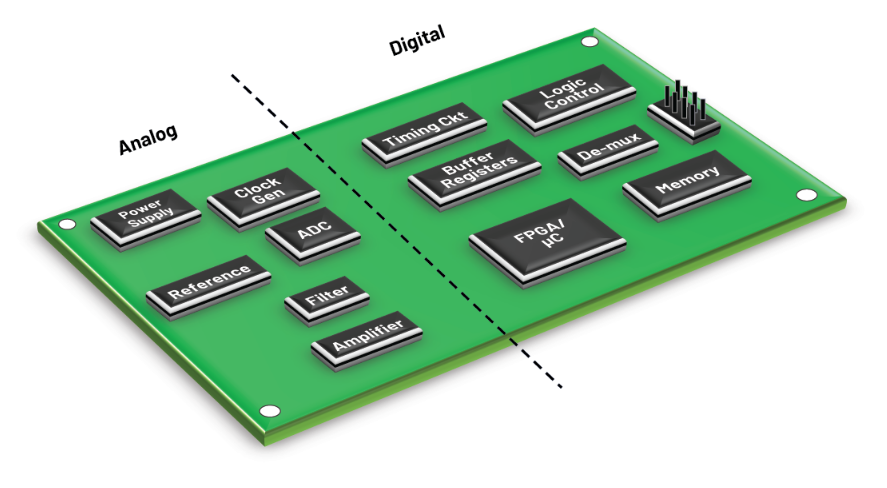

随着电子设备尺寸不断缩小,它们的内部电路必须同步缩小。产品小型化成为各行各业的显著发展趋势,这为工程师在空间受限的设计中完成合适的解决方案带来了新的设计难题。

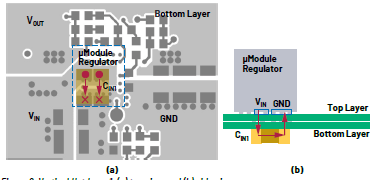

为了满足紧凑型电子设备日益严格的尺寸要求,集成电路设计人员将外部元件集成到器件内部,以最大程度地减少外部元件数量。在构建所有电子设备所需的各种电路中,缩小DC-DC 转换器的尺寸同样极具挑战性,因为它们无处不在(所有设备都需要电源),电源设计人员通常会面临这样一个现实,即缩小解决方案尺寸往往会对性能产生负面影响。

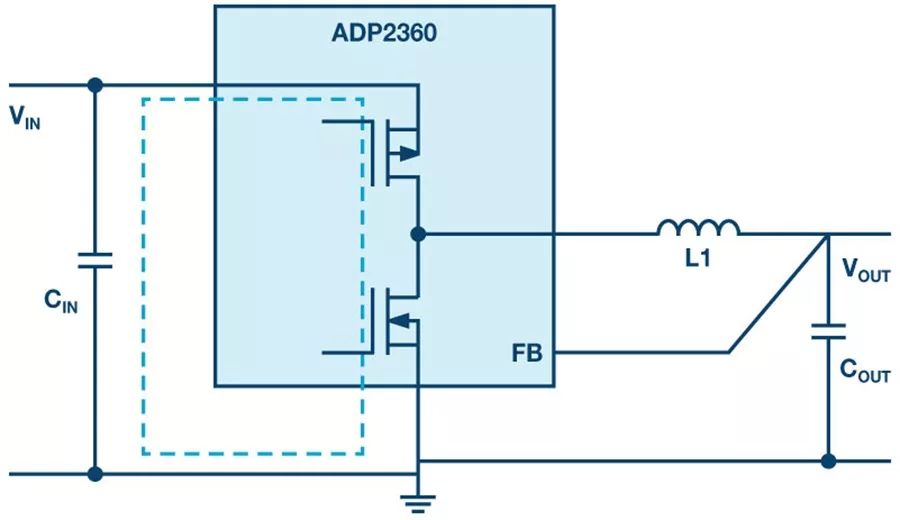

例如,能显著节省PCB面积的一种方法是采用单芯片DC-DC转换器,该转换器将经过精心选择的电源开关器件集成到IC封装之中,从而使所需外部元件减少为少量的无源器件。在许多情况 下,与外部电源开关控制器设计相比,紧凑型设计最终会带来不需要的结果,即在更小的空间中增加了功率损耗,从而产生更高的温升。为了避免产生的热量水平造成困扰,选择合适的单片式DC-DC转换器对于设计紧凑高效的电源系统至关重要。

1、2 MHz单芯片4开关DC-DC转换器和LED驱动器

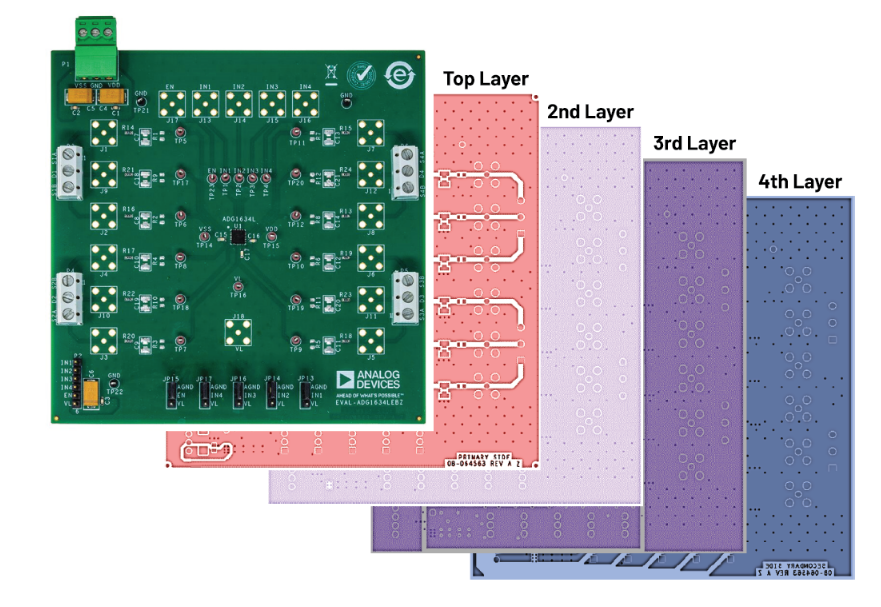

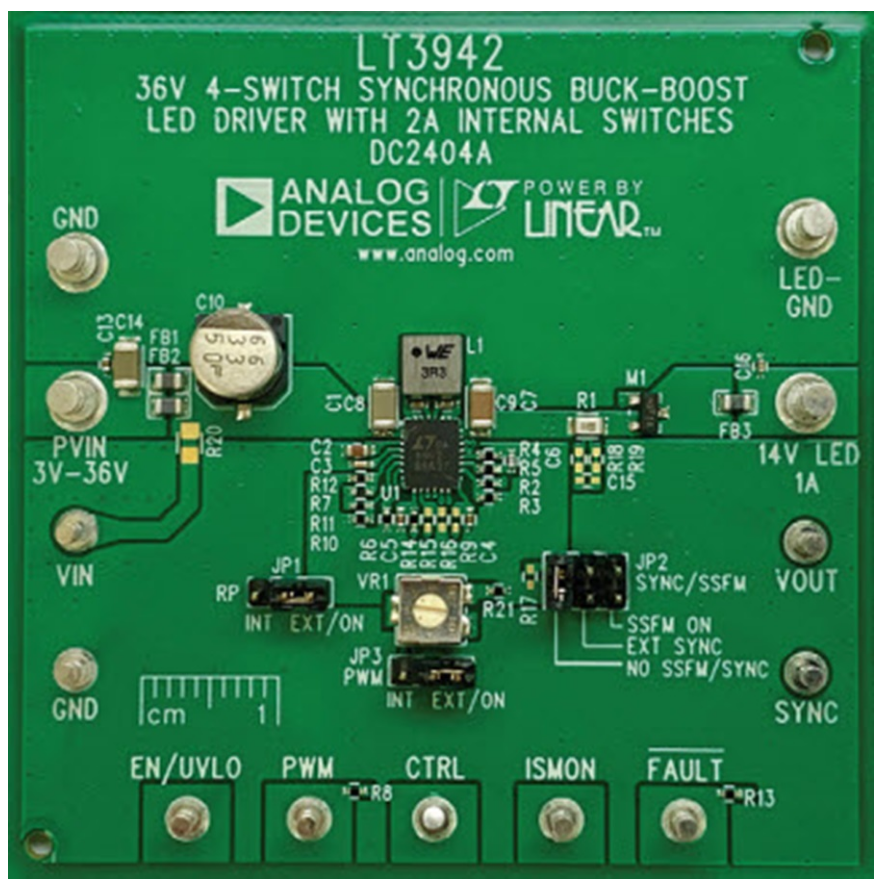

LT3942 是ADI非常通用的单芯片降压-升压稳压器IC之一。该升压-降压转换器能够应对在创建灵活紧凑的DC-DC转换器解决方案的同时不会牺牲性能的挑战。LT3942将四个40 V/2 A电源开关、 两个栅极驱动器自举二极管及其所有的控制和驱动器电路集成到一个4 mm × 5 mm小型QFN封装中。由于具有高达2 MHz工作开关频率能力,因此可以最大程度地减小外部元件的尺寸,节省 PCB空间,同时为各种DC-DC转换器提供了高带宽工作性能。

LT3942具有与 LT8390A/LT8391A 系列降压-升压控制器IC相同的峰值电流模式控制方案,并且能够在2开关升压、4开关降压-升压(升压-降压)和2开关降压工作模式之间无缝转换。转换器监测并比较其输入和输出电压,以确定正确的工作模式。当 PVIN:PVOUT 的比率发生变化并迫使转换器转换模式时,LT3942保持稳压作用,同时可以在开关对之间智能切换控制。

除了通过多种 PVIN:PVOUT组合来调节输出电压之外,LT3942还可以配置为调节输入或输出电流,以用于恒定电流调节应用。来自ISMON引脚的电流监控反馈提供了一个与实测电流成比例的缓冲电压输出,从而允许连接的电路监控实测的电流水平。这种调节电流或电压的能力使LT3942非常适合用作LED驱动器、紧凑型电池充电器、微型太阳能电池板供电的转换器或通用稳压器。

2、14 V、1 A LED驱动器

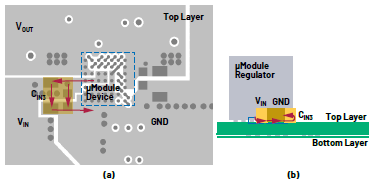

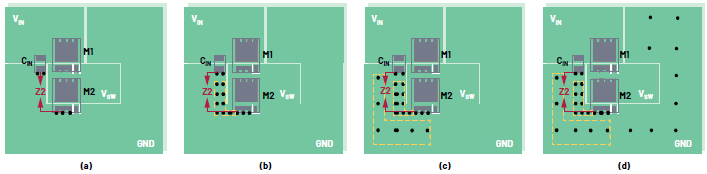

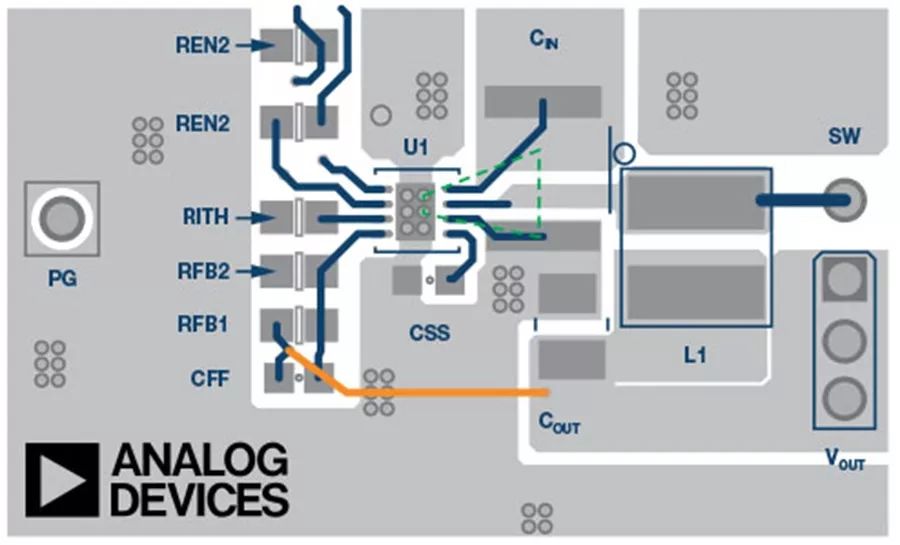

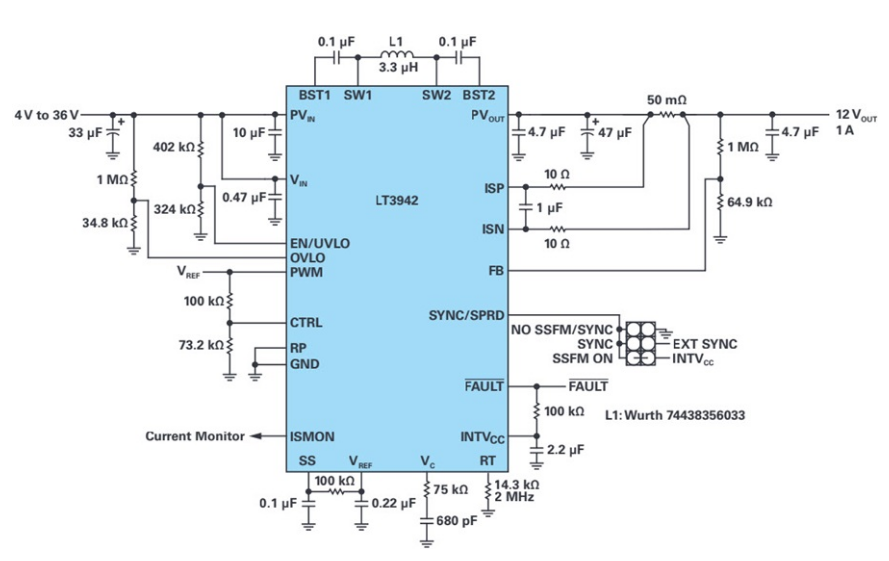

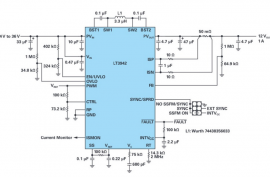

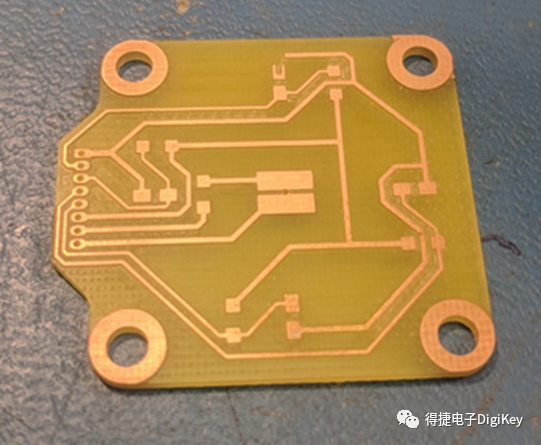

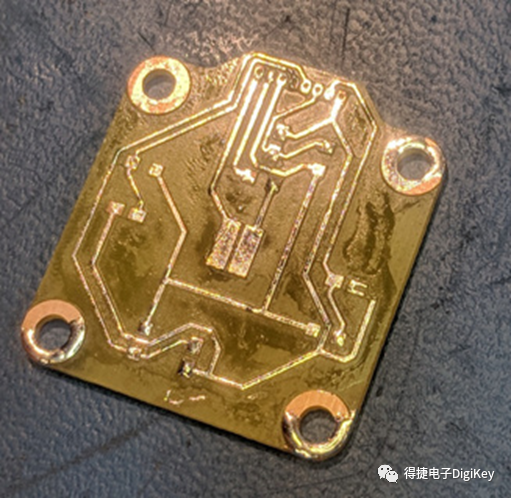

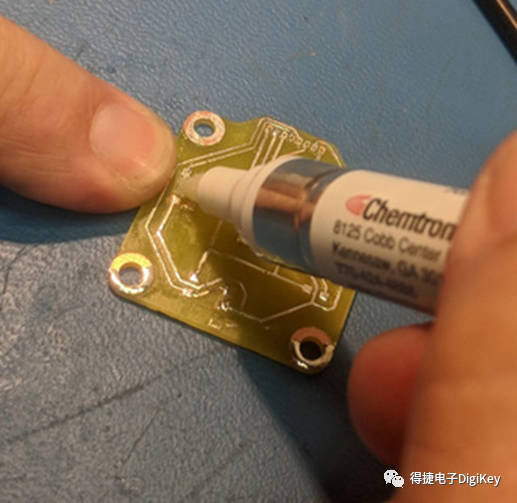

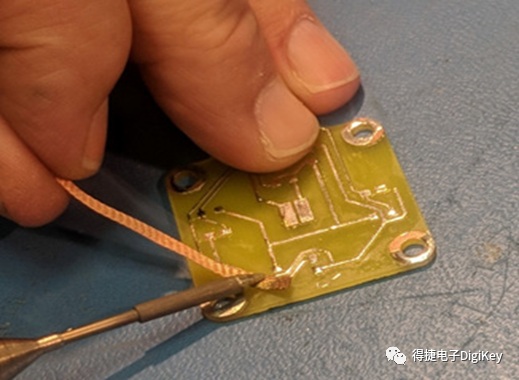

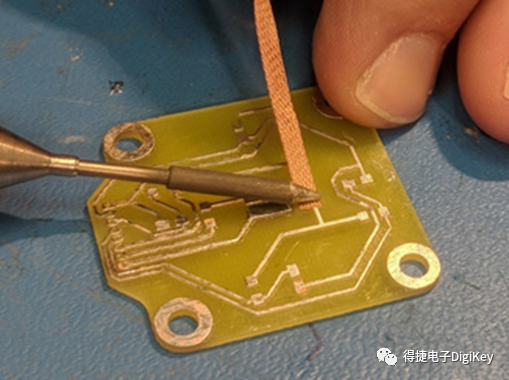

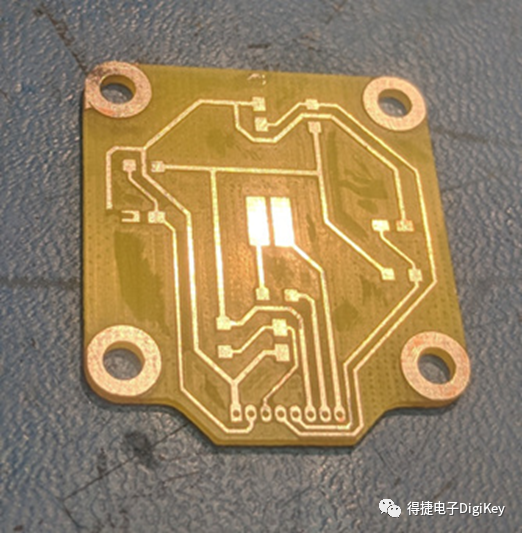

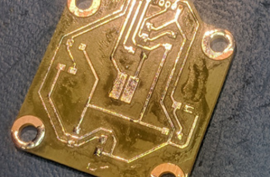

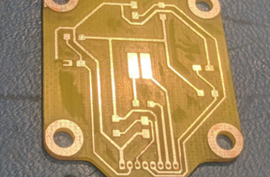

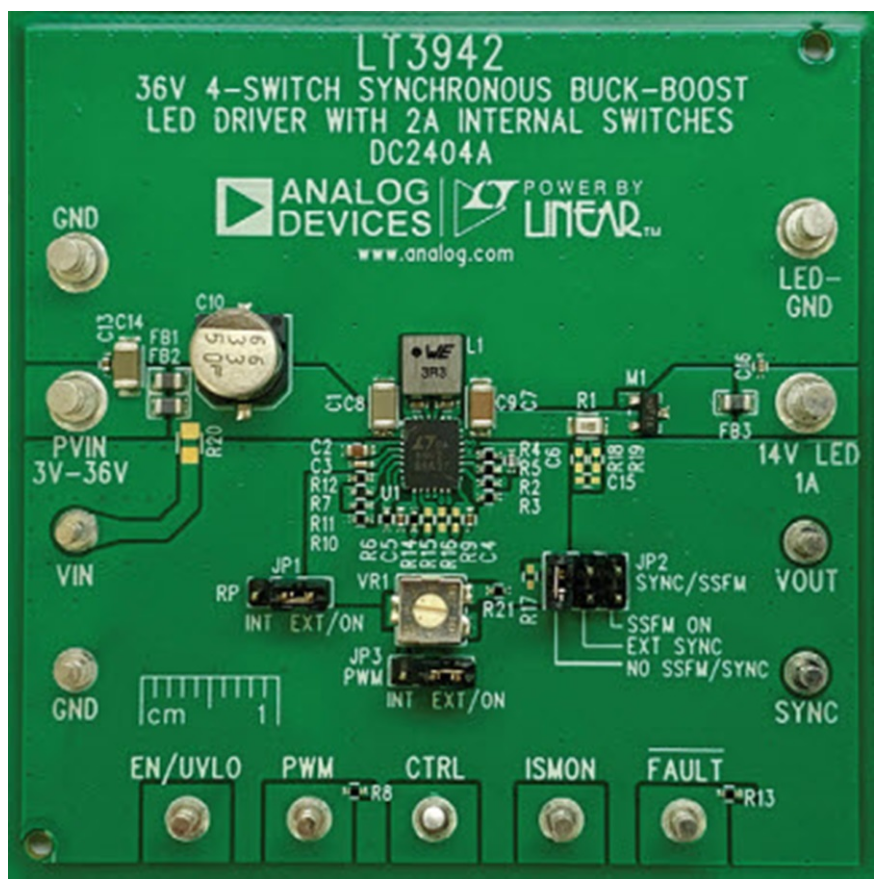

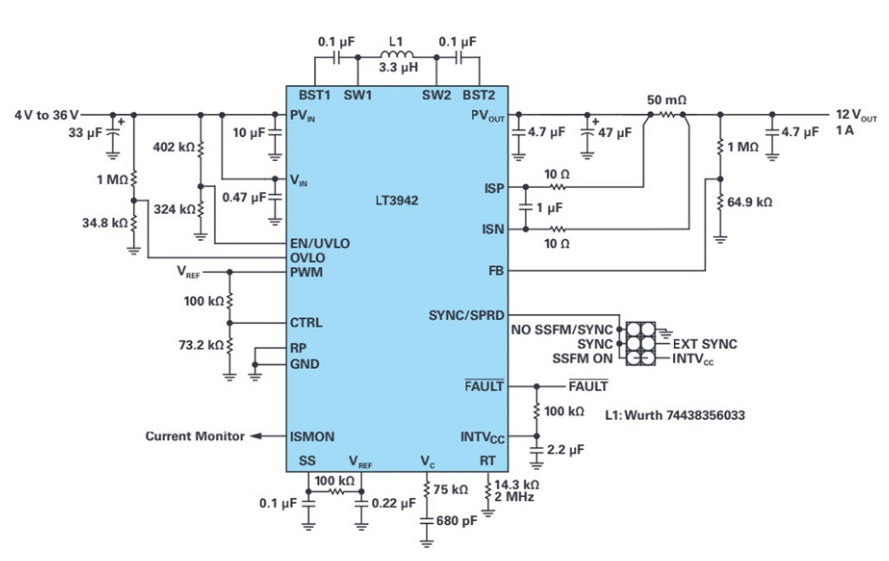

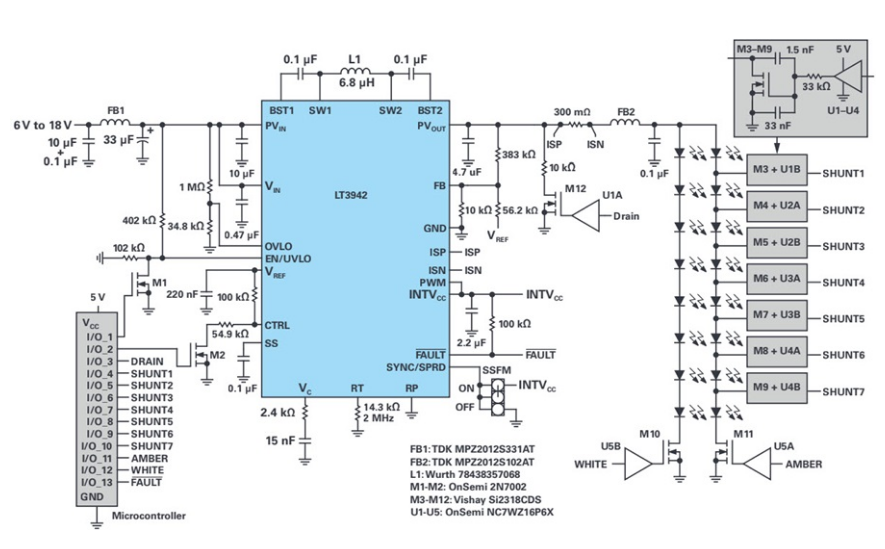

图1显示了基于LT3942的紧凑型LED驱动器的完整评估电路。该解决方案能够为四个(最高14 V)串联的一串白光LED提供1 A电流。最大功率输出的输入电压范围为7 V至36 V,低工作电流时可降至4 V,非常适合未稳压的汽车输入电源。该解决方案中的LT3942的工作开关频率为2 MHz,因此可以使用相对较小的电感和电容。所以完整的LED驱动器解决方案适合15 mm × 15mm 的PCB尺寸,所有元件都位于电路板的同一面(包括IC)。

图1. 这款基于LT3942的演示电路(DC2404A)展示了一种高性能、紧凑型DC-DC稳压器解决方案,专门用来在这种情况下驱动LED。

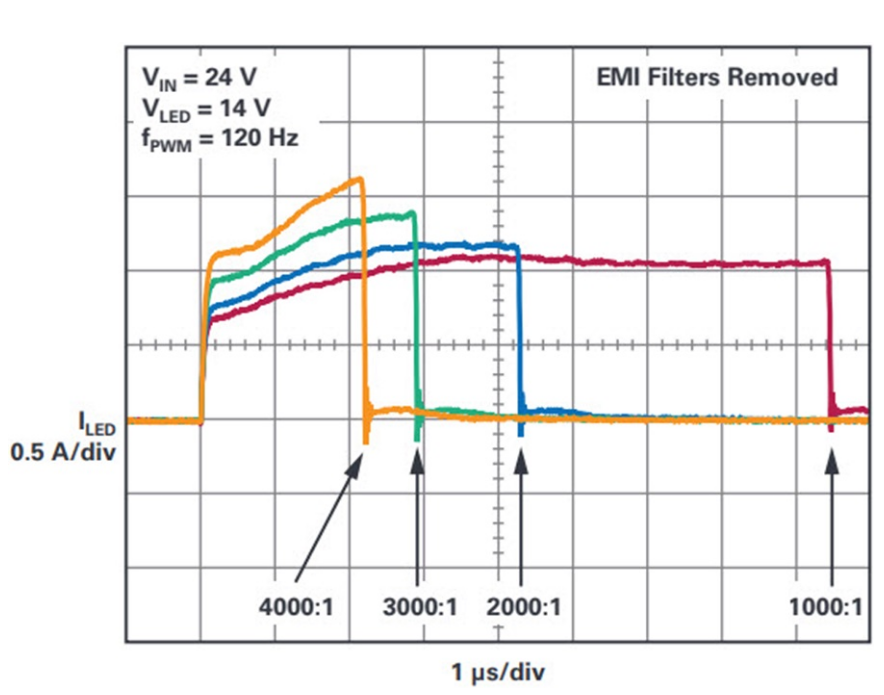

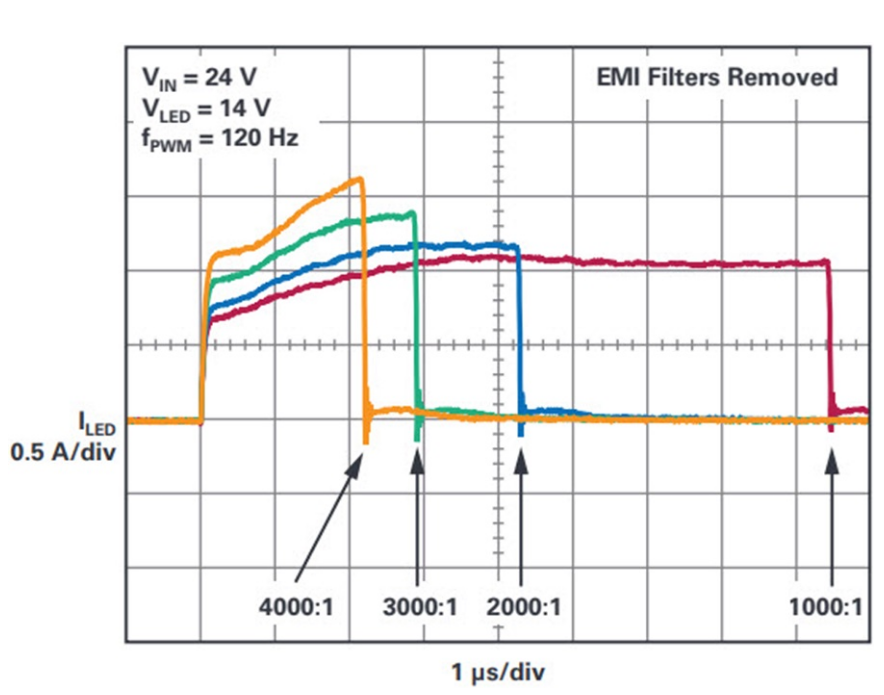

该解决方案还具有高带宽工作性能,可以快速调节输出电流。当在降压模式下工作时,LT3942使用外部PWM源对LED进行100Hz无闪烁调光,从而实现高达5000:1的调光比。如果没有外部 PWM源,也可以使用其内部PWM调光功能实现LT3942调光。内部调光提供高达128:1的调光功能,无需任何外部PWM信号源,仅需一个电阻即可设置调光频率,以及一个直流电压来控制输出电流的占空比。与大多数ADI Power的LED驱动器一样,LT3942还具有模拟调光功能,通过在CTRL引脚上施加直流电压可提供高达20:1的模拟调光。可以将模拟和PWM调光组合使 用,以实现比单独使用任何一种方法更高的有效调光比。

3、展频用于降低EMI峰值

为了帮助创建一个低噪声DC-DC转换器系统,LT3942内置一个可选展频(SSFM)功能。SSFM一旦启用,会在由RT电阻设置的值至高达25%的额外开关频率之间扫描开关频率。该扫描动作可以 在宽频谱范围内分散由开关引起的辐射,而不是将这些辐射集中在窄带中,从而降低整体的EMI峰值。SSFM与输入和输出EMI滤波器结合使用时,有助于降低宽频率范围内的EMI,从而更易于设计符合辐射标准的系统。

4、12 V、1 A稳压器

LT3942不只限于驱动LED。它是一款功能强大的紧凑型稳压器,非常适合解决从宽范围未稳压电源产生稳定输出的问题。图4中所示的12 V、1 A稳压器设计与图2中的14 W LED驱动器解决方案相似,但做了一些小改动。与LED驱动器应用一样,稳压器可以在很宽的输入电压范围内维持输出调节,可在电压低至7 V的条件下提供全输出功率,并在电压低至4 V的条件下维持低输出功率工作。

图2. DC2404A利用LT3942创建了一个紧凑型14 W LED驱动器应用,可在宽输入范围提供稳定的输出电流。

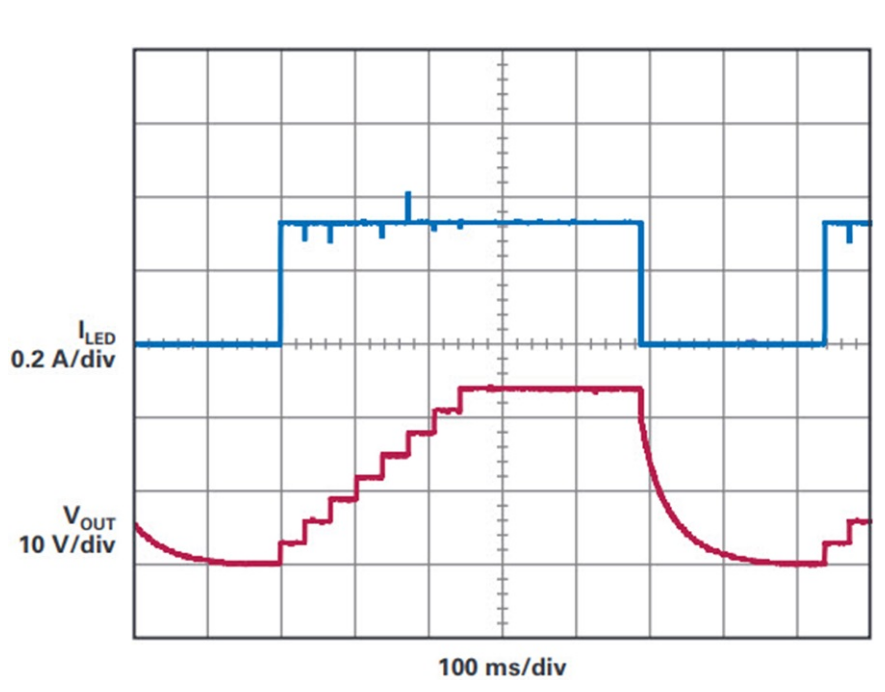

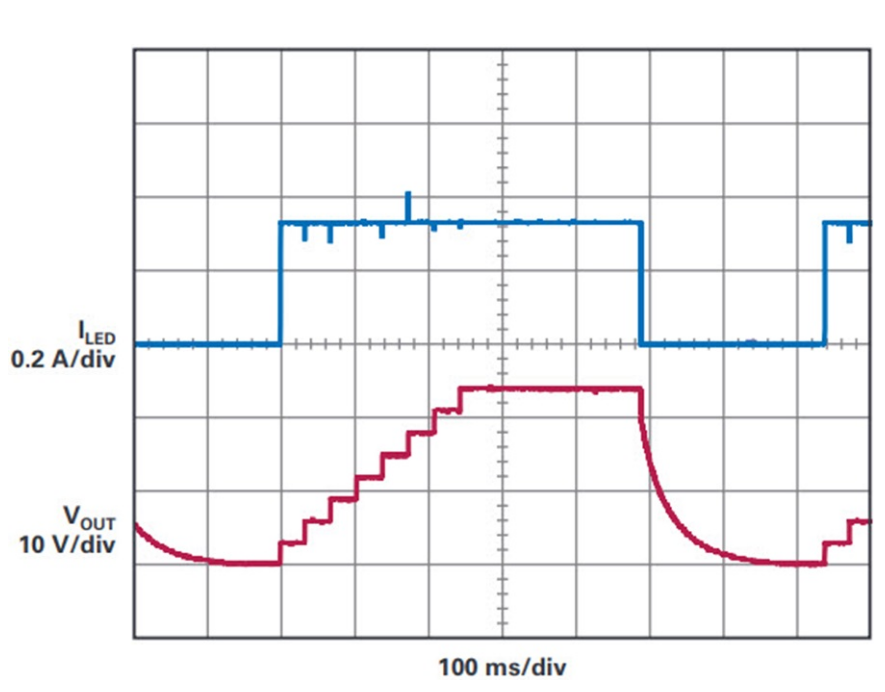

图3. LT3942的高带宽工作性能有助于LED照明应用在宽动态亮度范围内实现高比率PWM调光。无需EMI滤波器,DC2404A在120 Hz时可实现高达4000:1的调光,而在100 Hz时则可实现高达5000:1的调光。

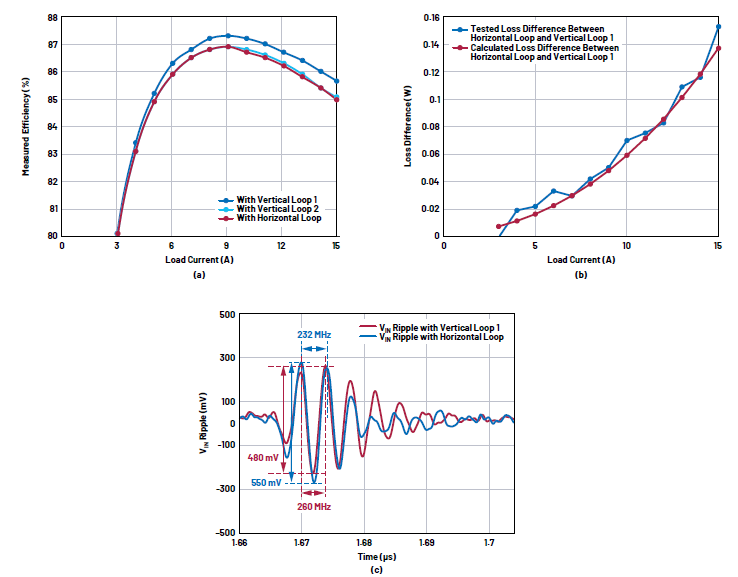

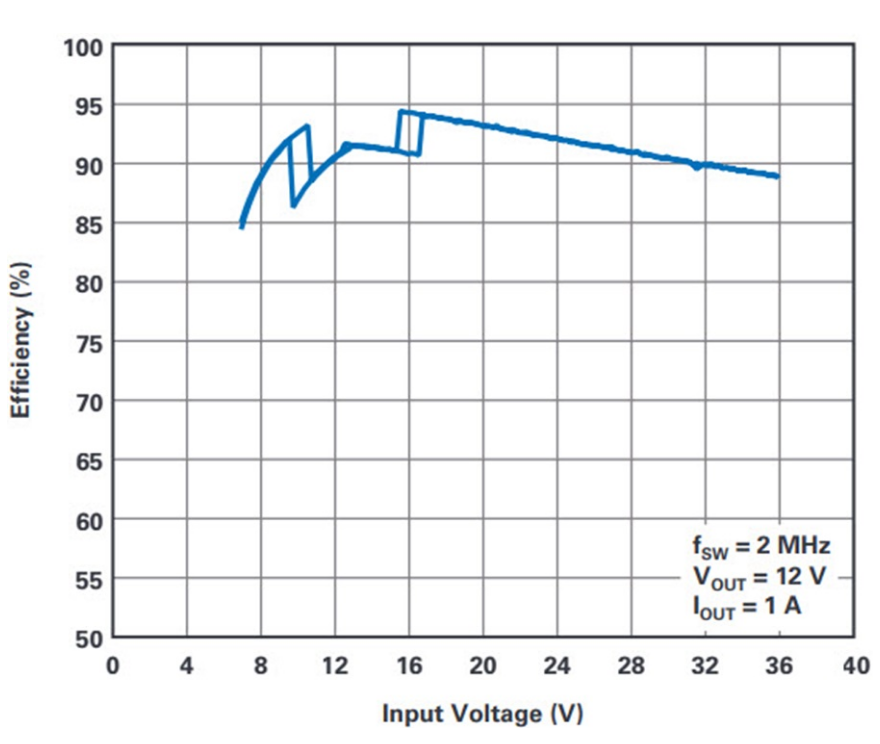

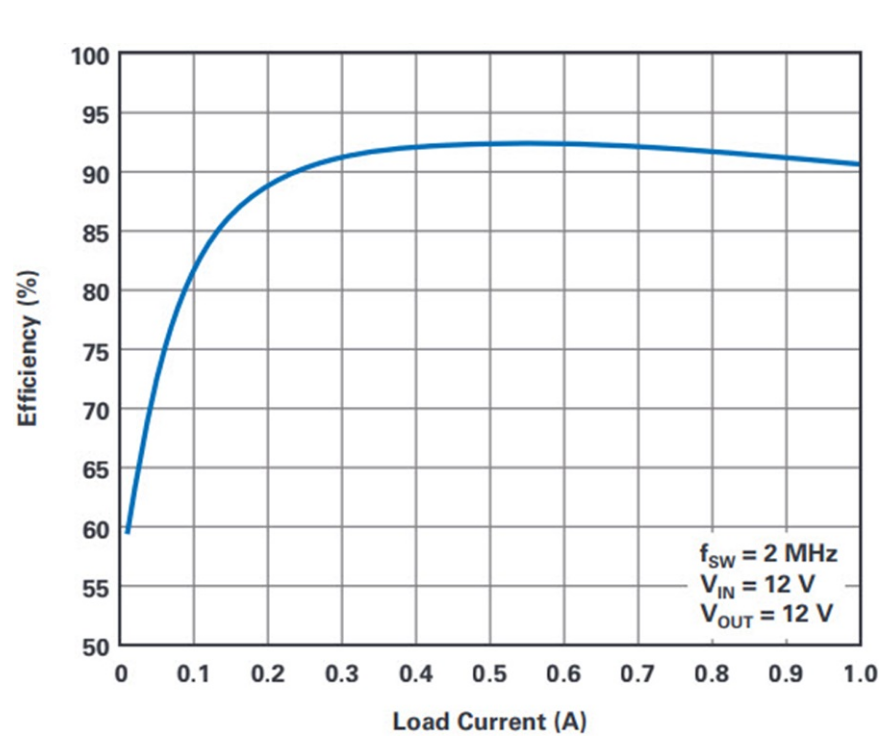

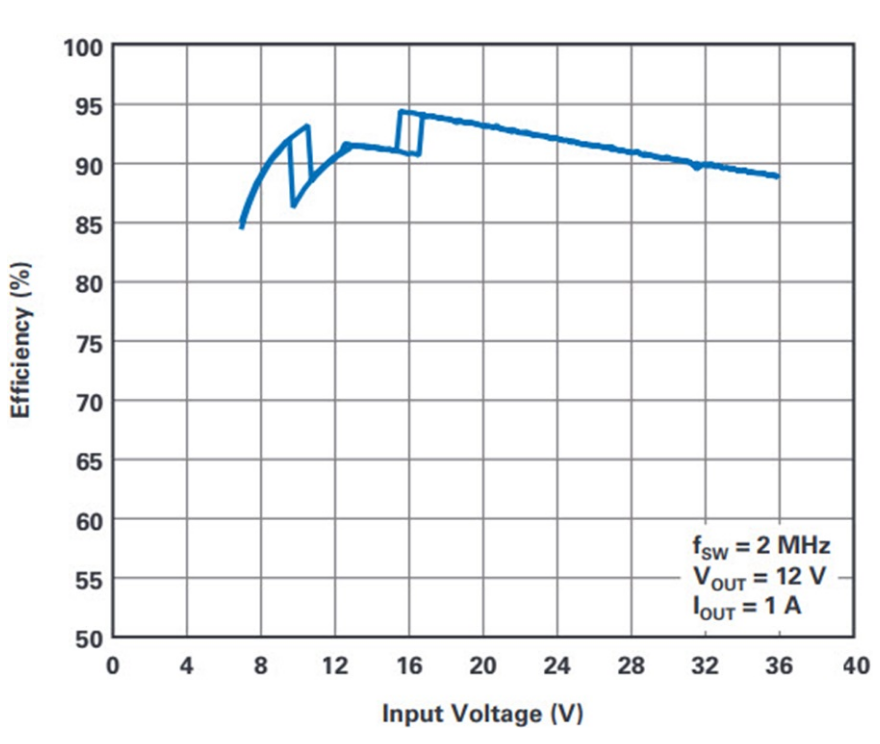

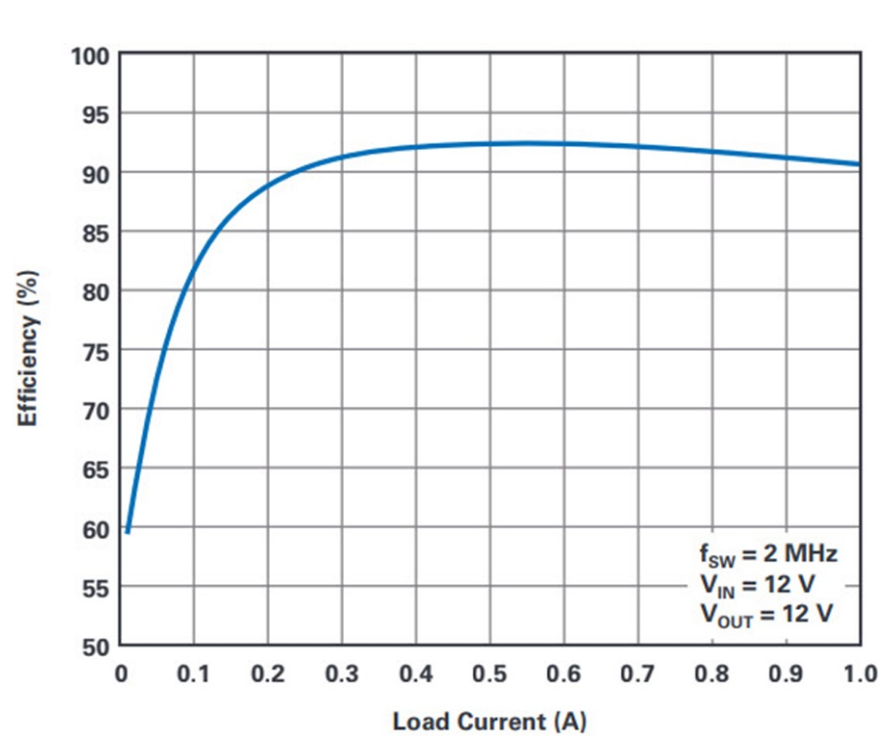

图4中的效率曲线表明,即使工作开关频率为2 MHz时,LT394212 V稳压器也具有接近95%的出色峰值效率,而在其大多数输入电压范围内的效率为85%或更高。即使以其总输出功率的十分 之一为其输出供电,也可保持80%以上的效率,这表明该器件在轻负载条件下仍可高效运行。

(a). Input Voltage Efficiency Sweep.

(b). Load Current Efficiency Sweep.

图4. 配置为12 W稳压器的LT3942在宽输入范围内具有出色的电压调节和负载效率特性。

LT3942的电流检测和控制特性使其不仅适合于LED调光控制,而且也能在需要电压调节和电流控制的其他情况下出色地工作。将检测电阻配置在输出端时,可以很轻松地将LT3942配置用作紧凑型恒流、恒压电池充电器。对于具有严格输入电流限制的应用,例如由小型电池、电容组或光伏电池供电的电路,可以将监测电阻移至稳压器的输入侧,从而为系统提供输入电流限制和监控。LT3942可从CC模式无缝转换为CV模式(反之亦然),确保输入和/或输出始终稳定。

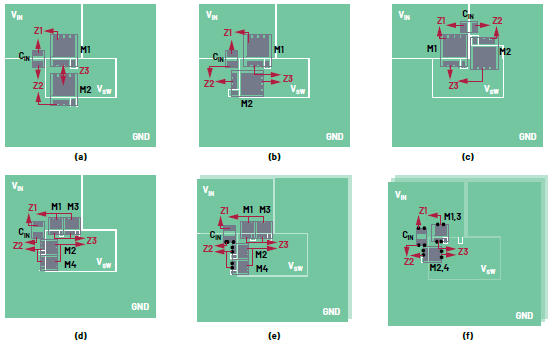

5、汽车顺序点亮转向信号和装饰性照明

在新型豪车和高性能汽车上常见的动画式顺序点亮转向信号灯正在迅速普及,逐步取代传统的闪烁式指示灯。早期的顺序点亮转向信号的实现采用多个降压转换器或线性稳压器为转向信号灯组中的LED供电,导致解决方案复杂、相对低效且过于庞大,极大地限制了照明设计的应用领域。减少所需功率IC的数量,使用单个高效器件,是扩大照明设计人员选择范围的明显方式。

单个转换器解决方案需要的器件能够对各种LED组合(照明设计中会出现从所有LED点亮到单个LED点亮,以及介于前两者之间的各种其他组合)的串电压维持输出调节。随着动画灯在连接 的LED的各种配置中变化时,输入电压会高于、低于或等于输出电压。这种类型的应用需要一个升压-降压转换器,该转换器可以智能地选择工作模式并在工作模式之间无缝转换,同时维持 输出调节。LT3942的降压-升压拓扑和高带宽工作性能使它能够轻松操纵这些变化而不会出现毛刺。

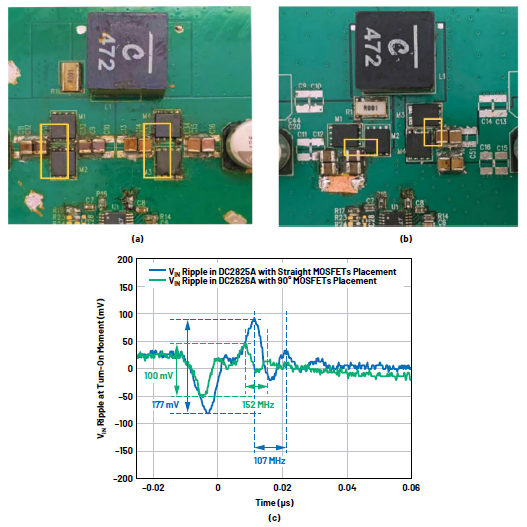

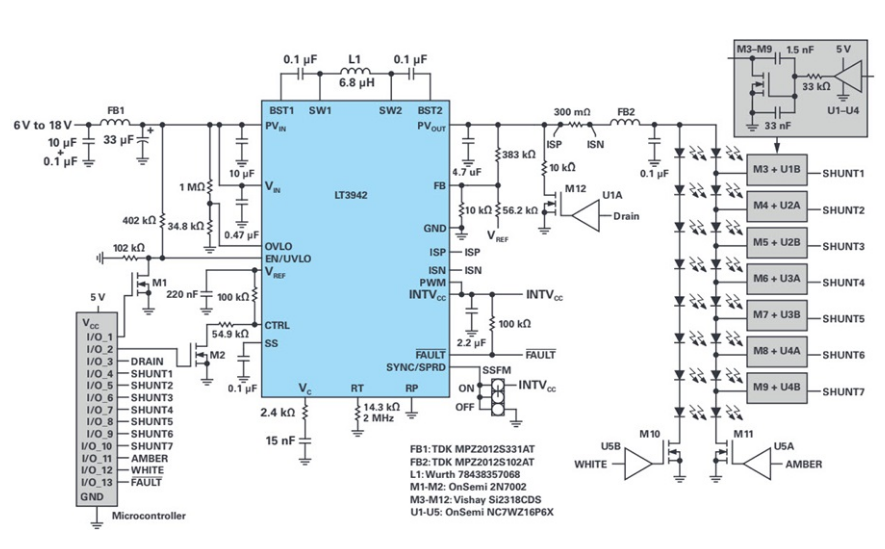

图5所示的顺序点亮转向信号设计采用LT3942从汽车电池以330mA电流为八个LED供电,并可选择为一串琥珀色LED(用于转向信号灯操作)、一串白色LED(用于日间行车灯)或其他装饰性 照明(用于前灯/尾灯设计中)供电。

图5. 在顺序点亮转向信号应用中,每次点亮一个LED,从而迫使DC-DC转换器迅速适应新的 PVIN:PVOUT 组合。这对LT3942来说不是问题,因为它可在 顺序点亮转向模式期间从升压、降压-升压、降压工作模式无缝转换,从而确保在各种模式下维持稳定的LED电流。

微控制器充当用户输入的转向信号与照明系统之间的接口。这使照明设计人员(或最终用户,如果需要的话)能够完全控制执行LED动画顺序点亮所需的所有时序和信号,并且可以控制在 任何给定时间为哪种颜色的LED灯串供电。

在此设计中,在顺序点亮模式期间,每次向灯串导入一个转向信号LED,以产生转向信号。当LED由微控制器添加到灯串时,LT3942维持对输出电流的调节,以保持一致的光亮度。在所有 LED都点亮之后,LT3942停止开关操作,并拉低输出电压,使转换器设置为下一个顺序点亮周期做好准备。当转向信号未使用时,微控制器重新连至装饰照明LED串,并继续等待转向信号用户输入,这将两种照明功能组合到一个LED驱动器解决方案中。

6、小结

电子设备迫使工程师不断寻求更小的集成器件,以满足日益增长的空间受限需求。LT3942单芯片降压-升压转换器和LED驱动器集成了众多可节省空间的特性,以解决空间受限的电气设计 难题,同时不会牺牲性能。其单芯片设计和2 MHz的工作开关频率缩小了解决方案的尺寸,使其能够适用于紧凑的PCB设计中。该器件具有高度灵活性,既可以用作恒流调节器,也可以 用作恒压调节器,适合各式各样的应用。

对于需要低噪声电源以满足严格EMI要求的设计,LT3942的SSFM功能有助于降低传导发射和电磁辐射骚扰,其便捷的IC封装引脚排列可实现紧凑的开关热环路。这些特性以及宽输入范围, 可在设计人员面临紧凑型电源需求时,简化他们的工作。

来源:亚德诺半导体

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。