选MOS管,N沟道比P沟道的优势在哪?

本文中,DigiKey探讨 N 沟道与 P 沟道 MOSFET 的性能差异,分析为何 N 沟道更受青睐,助你选对元件。

本文中,DigiKey探讨 N 沟道与 P 沟道 MOSFET 的性能差异,分析为何 N 沟道更受青睐,助你选对元件。

mos在控制器电路中的工作状态:开通过程(由截止到导通的过渡过程)、导通状态、关断过程(由导通到截止的过渡过程)、截止状态。

MOS管为什么会被静电击穿?静电击穿是指击穿MOS管G极的那层绝缘层吗?击穿就一定短路了吗?JFET管静电击穿又是怎么回事?

MOS管中文名金属氧化物半导体绝缘栅场效应管。其输入阻抗高、开关速度快、热稳定性、电压控制电流等特性。IGBT中文名绝缘栅双极型场效应晶体管。是MOS管与晶体三极管的组合,MOS是作为输入管,而晶体三极管作为输出管。

在电子电路中,MOS 管和 IGBT 管会经常出现,它们都可以作为开关元件来使用,MOS 管和 IGBT 管在外形及特性参数也比较相似,那为什么有些电路用 MOS 管?而有些电路用 IGBT 管?

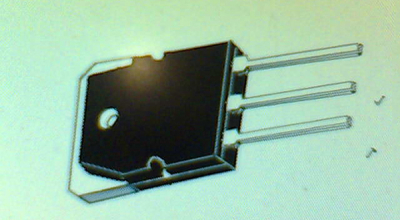

MOSFET的击穿有哪几种?Source、Drain、Gate,场效应管的三极:源级S 漏级D 栅级G,(这里不讲栅极GOX击穿了啊,只针对漏极电压击穿)。

在栅源短接,漏-源额定电压(VDSS)是指漏-源未发生雪崩击穿前所能施加的最大电压。根据温度的不同,实际雪崩击穿电压可能低于额定VDSS。

电源的输入部分,为了防止误操作,将电源的正负极接反,对电路造成损坏,一般会对其进行防护,如采用保险丝,二极管,MOS管等方式,这里就稍微做一下梳理总结。

9、为什么在E-MOSFET的栅-漏转移特性上,随着栅-源电压的增大,首先出现的是饱和区电流、然后才是线性区电流?

【答】E-MOSFET的栅-漏转移特性如图1所示。在栅-源电压VGS小于阈值电压VT时,器件截止(没有沟道),源-漏电流电流很小(称为亚阈电流)。

1. 为什么E-MOSFET的阈值电压随着半导体衬底掺杂浓度的提高而增大?而随着温度的升高而下降?