为敏感电路提供过压及电源反接保护

为了隔离负电源电压,设计人员惯常的做法是布设一个与电源相串联的功率二极管或 P 沟道 MOSFET。

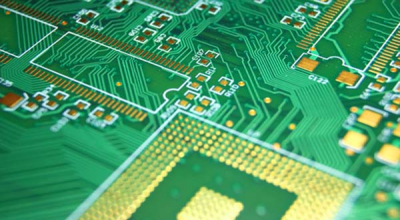

电路设计是创建电子电路的过程,旨在实现特定的功能或任务。电路可以是数字电路、模拟电路、混合信号电路或射频电路,根据应用的不同。

为了隔离负电源电压,设计人员惯常的做法是布设一个与电源相串联的功率二极管或 P 沟道 MOSFET。

减少后级电源对前级的影响,防止电源正负接反烧坏后级电路,防止电源关电时电流倒灌,但经过二极管有0.4V左右压降,需要考虑经过0.4V降压后会不会低于后级电路的正常工作电压。

单片机是嵌入式系统的核心元件,使用单片机的电路要复杂得多,但在更改和添加新功能时,带有单片机的电路更加容易实现,这也正是电器设备使用单片机的原因。

单片机是嵌入式系统的核心元件,使用单片机的电路要复杂得多,但在更改和添加新功能时,带有单片机的电路更加容易实现,这也正是电器设备使用单片机的原因。

许多系统必须能够自动断开正在运行的电路的电源,此类系统包括雷达及X射线系统的高压电源的热关断,关断控制能够限制上电及热插拔期间的浪涌电流,确保板卡在上电之前处于就绪状态。总之,发生任何系统故障时电源都应保持关闭。

针对电气控制产品的特点,本文讨论了几种单片机I/O的常用驱动和隔离电路的设计方法,对合理地设计电气控制系统,提高电路的接口能力,增强系统稳定性和抗干扰能力有实际指导意义。

接口电路的设计在电单片机应用场合中还是很重要的,因为如果接口电路没有设计好,严重就会烧芯片,或者烧芯片IO口,轻者就会导致工作紊乱,工作不正常。

意法半导体的 L4985A/B和L4986A/B功率因数校正(PFC) 升压转换器集成 800V 启动电路,以及意法半导体专有的实用的辅助功能,有助于简化应用设计,提高设计灵活性。

在很多场合,已经出现了越来越多的单片机产品代替传统的电气控制产品。单片机其控制功能通过软件指令来实现,其硬件配置也可变、易变。因此,一旦生产过程有所变动,就不必重新设计线路连线安装,有利于产品的更新换代和订单式生产。

对于数字电路来说,VCC是电路的供电电压,VDD是芯片的工作电压(通常Vcc>Vdd),VSS是接地点。