相关阅读:

RA2快速设计指南 [7] 模块停止功能,中断控制单元与低功耗

RA2快速设计指南 [8] 外部总线、SDADC24和OPAMP

16. 一般布线实践

16.1 数字域与模拟域

Renesas RA2微控制器产品主要有三种类型的引脚功能:电源、数字和模拟。

通常,电源引脚专门用于电压和参考输入,没有多种功能。电源引脚通常专门用于MCU内的特定部分或域。例如,MCU的主电源电压将为数字内核、许多数字外设功能和许多数字I/O引脚供电。可以将数字域定义为数字电路、数字I/O引脚以及相关的电源引脚。指定用于模拟功能的电源引脚(例如AVCC0和相关的AVSS0)在MCU内部提供特定的模拟电路,这类模拟电路与数字域电路分开。可以将模拟域定义为模拟电路、模拟I/O引脚以及相关的电源引脚。

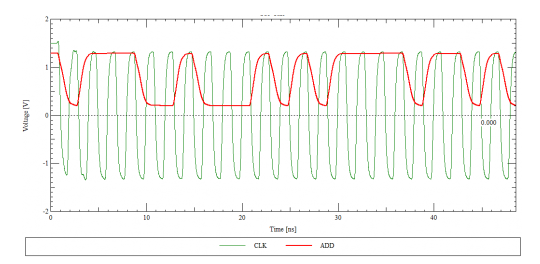

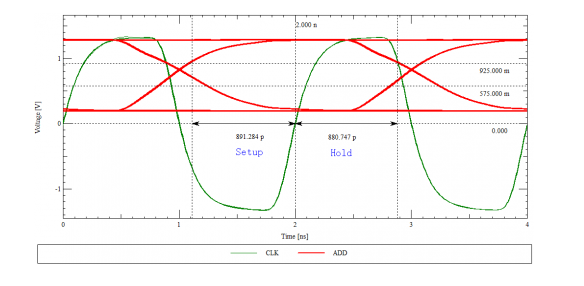

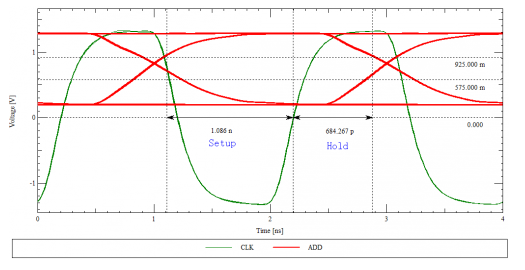

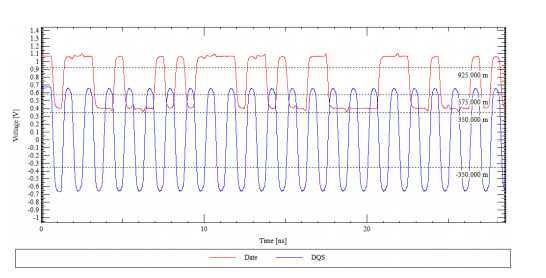

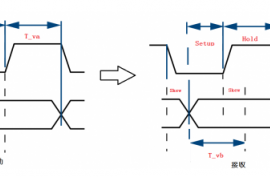

数字信号通常是与周期性时钟相关联的重复切换模式。数字信号上的跳变往往是相对尖锐的边沿,同时跳变之间保持稳定的高电平或低电平。在指定的时间范围内,每个信号必须在可接受的电压大小下处于稳定状态,称为逻辑状态。通常使用时钟的边沿跳变以预定的时钟间隔对信号状态进行采样,以评估相关的数据信号。只要电平保持在指定范围内,数字信号电压值的小幅度变化通常是可以接受的。但是,如果数字信号受到可能会对其造成严重影响的较大外部作用,则可能会在对数据进行采样时引起错误的逻辑状态。

模拟信号通常截然不同。模拟信号可能是周期性的,但模拟信号的评估通常是在一定范围内而不是逻辑状态下测量电压。根据特定的触发事件对模拟信号的电压大小进行采样,然后使用MCU中的模拟电路处理得到的测量结果。模拟测量的精度与采样电压值的精度直接相关。任何可能会略微改变模拟输入信号电压值的非预期外部作用,都可能影响测量的准确性。

由于Renesas RA2 MCU产品的I/O引脚的高度复用特性,许多I/O引脚都可用于实现模拟或数字功能。这可能会导致数字和模拟功能发生重叠,并造成数据错误。

为了尽可能地减少数字信号域和模拟信号域之间的潜在问题,请考虑以下准则:

• 在分配I/O引脚功能时,选择的引脚功能应尽量使模拟引脚和数字引脚在物理上分开。

• 每个模拟信号应尽可能与所有其他信号分开。

• PCB布线应尽可能隔离每个模拟信号。避免在同一区域内连接其他任何信号走线,无论是模拟信号还是数字信号。

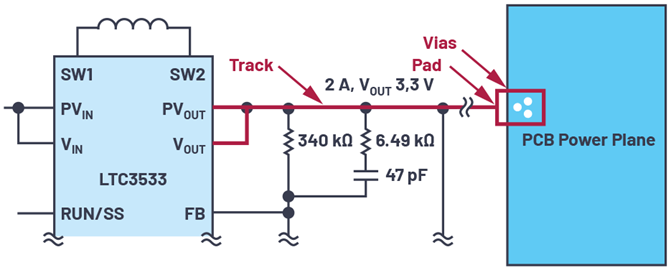

• 确保模拟电源电压和模拟参考电压包含适当的交流滤波器。可以采用在MCU电压引脚附近放置的形式

建议使用的电容,或使用适当的感应滤波器。此举旨在提供很少甚至没有电压纹波的电源电压和参考电压。

• 在PCB设计中使用专用电源层时,避免在模拟电压区域内连接数字信号走线,并避免在数字电压区域内连接模拟信号走线。

对于灵敏度较高的应用,强烈建议使用仿真工具评估特定的设计,以了解电路设计对性能的影响。例如,这可能包括诸如精密传感器设计或超高速数字总线接口之类的应用。有关每种外设功能的特定要求,请参见《硬件手册》中的“电气特性”一章。

16.2 高速信号设计注意事项

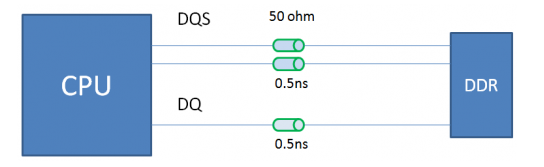

随着数字信号时钟速度的增加,外部刺激对这些信号的影响会变得更加明显。某些外设功能可以归类为“高速”数字信号。对于高速数字信号,还应考虑其他设计注意事项。

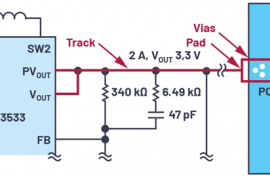

在发生串扰时,一个信号上的跳变会对附近的另一个信号产生感应影响。当这种串扰效应足够强时,第一个信号可能会导致第二个信号上发生错误。为了减少串扰的影响,请使用以下一般PCB布线准则:

• 为同一布线层上的已连线信号之间提供足够的空间。通常,在同一数字组的信号之间至少保留一倍走线宽度的空间,而在不同数字组的信号之间至少保留3-5倍走线宽度的空间。

• 为同一布线层上的时钟信号和数据信号之间提供额外的空间。通常,在时钟和任何其他数字信号之间至少要保留3-5倍走线宽度的空间。

• 避免在任何相邻的布线层上并行连接数字信号走线。如果必须在相邻的信号层上连接信号,请尽可能尝试仅使用正交叉走线。

如有可能,请在信号层之间使用电源层或接地层来分隔PCB信号层。电源层或接地层的单芯铜线可以用作数字信号的“屏蔽”。

每个标准化接口都有特定的要求。为确保PCB设计不会出现信号串扰问题,强烈建议设计每个接口时都参考相关标准。

16.3 信号组选择

某些引脚名称带有附加的 _A、_B、_C、_D、_E 或 _F 后缀来表示信号组。对RA2产品而言,在分配功能时可忽略这些后缀,为每个功能信号选择最方便的引脚分配。

请参见《硬件手册》中“I/O端口”一章的“每种产品的外设选择设置”和“PmnPFS寄存器设置的注意事项”部分。

17. 参考资料

在编写本《快速设计指南》时,参考了以下文档,您可点击此处进入瑞萨电子官网了解更多内容。

网站和支持

如需了解RA系列的关键元素、下载组件和相关文档以及获得支持,请访问以下链接:(如微信中无法打开,请复制网址后在浏览器中打开查看)

RA产品信息

https://www.renesas.cn/cn/zh/products/microcontrollers-microprocessors/r...

RA产品支持论坛

https://community-ja.renesas.com/zh

RA灵活配置软件包

https://www.renesas.cn/cn/zh/software-tool/flexible-software-package-fsp

技术支持

瑞萨MCU中文支持社区

https://zh-support.renesas.com/dashboard

来源:瑞萨MCU小百科

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。