如何将MCU与FPGA进行配对达到提高系统效率的目的

本文将快速回顾一些的应用,其中FPGA和MCU“配对”,以展示如何通过降低功耗,减小电路板空间,提高处理性能或接口灵活性来提高系统效率,从而显着改善您的下一个设计。

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

本文将快速回顾一些的应用,其中FPGA和MCU“配对”,以展示如何通过降低功耗,减小电路板空间,提高处理性能或接口灵活性来提高系统效率,从而显着改善您的下一个设计。

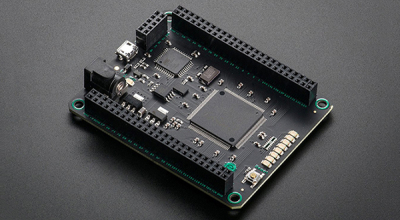

紫光同创携手电子创新网联合推出紫光同创PGL22G开发平台试用活动。通过试用活动,一方面让更多应用用上本土FPGA,另一方面,也通过大家的反馈开发出更好的FPGA器件,欢迎FPGA应用开发者,高校师生和研究人员踊跃报名,申请试用!

在去年电子创新网举办的2019FPGA应用创新论坛上,一家低调的FPGA新玩家引发了大家极大的兴趣,它就是EFINIX公司,为何全球FPGA领头羊赛灵思会投资这家公司?它的创始人团队有多牛?他们捣鼓出来的FPGA新架构到底有什么独特性?本文为你详细介绍。

12月19日,在ELEXCON 2019深圳国际电子展召开第一天,由电子创新网主办的2019FPGA创新应用论坛也在会展中心同期开幕,来自全国各地的150多位FPGA开发业者和国内领先FPGA厂商紫光同创、安路科技、西安智多晶、雪湖科技,Efinix等公司就本土FPGA发展未来趋势和挑战进行了深入交流…

现有的数控系统中多采用工控机加运动控制卡的计算机数控系统方案进行运动控制器的设计。随着工控机整体功能日趋复杂,对运动控制系统的体积、成本、功耗等方面的要求越来越苛刻。现有计算机数控系统在运动控制方面逐渐呈现出资源浪费严重、实时性差的劣势。此外,数控系统的开放性、模块化和可重构设计是目前数控技术领域研究的热点,目的是为了适应技术发展和便于用户开发自己的功能。

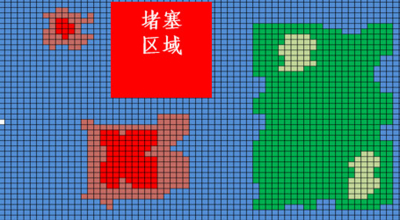

介绍了一种基于fpga的多轴控制器,控制器主要由arm7(LPC2214)和fpga(EP2C5T144C8)及其外围电路组成,用于同时控制多路电机的运动。利用Verilog HDL硬件描述语言在fpga中实现了电机控制逻辑,主要包括脉冲控制信号产生、加减速控制、编码器反馈信号的辨向和细分、绝对位移记录、限位信号保护逻辑等。

作者:赵厉,张志国,唐芳福

1. 概述

现场可编程门阵列即FPGA,是从EPLD、PAL、GAL等这些可编程器件的基础上进一步发展起来的。作为专业集成电路领域中的半定制电路而出现的FPGA,不但解决了定制电路的不足,而且克服了原有可编程器件因门电路数有限的而产生的缺点。FPGA 的使用十分的灵活,同一片FPGA 只要使用不同的程序就能够达到不同的电路功能。

在电子工程,资源勘探,仪器仪表等相关应用中,频率计是工程技术人员必不可少的测量工具。频率测量也是电子测量技术中最基本最常见的测量之一。不少物理量的测量,如转速、振动频率等的测量都涉及到或可以转化为频率的测量。目前,市场上有各种多功能、高精度、高频率的数字频率计,但价格不菲。

1引言

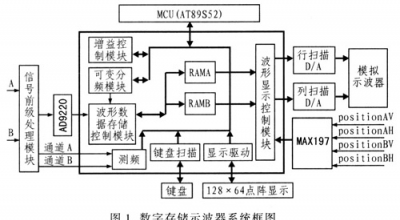

与传统模拟示波器相比.数字存储示波器不仅具有可存储波形、体积小、功耗低,使用方便等优点,而且还具有强大的信号实时处理分析功能。在电子测量领域,数字存储示波器正在逐渐取代模拟示波器。但目前我国使用高性能数字存储示波器主要依靠国外产品,而且价格昂贵。因此研究数字存储示波器具有重要价值。借于此,提出了一种简易数字存储示波器的设计方案,经测试,性能优良。