ET6000系列 MCU/DSP 在微逆场景下的应用

翌创微电子ET6000 MCU/DSP系列芯片内置Arm®/Cortex®-M系列中最高性能的32位处理器内核Cortex®-M7,具有高算力、大容量非易失性嵌入式存储、高性能模拟外设、配置灵活的高精度PWM以及快速关断的系统级保护等特性,提供卓越的实时处理与环路控制性能,特别适用于各种功率转换应用,如光伏逆变、储能变换、电机控制以及充电桩等,同时满足有功能安全要求的汽车级应用,可为客户提供高性能的数字能源主控芯片解决方案。

翌创微电子ET6000 MCU/DSP系列芯片内置Arm®/Cortex®-M系列中最高性能的32位处理器内核Cortex®-M7,具有高算力、大容量非易失性嵌入式存储、高性能模拟外设、配置灵活的高精度PWM以及快速关断的系统级保护等特性,提供卓越的实时处理与环路控制性能,特别适用于各种功率转换应用,如光伏逆变、储能变换、电机控制以及充电桩等,同时满足有功能安全要求的汽车级应用,可为客户提供高性能的数字能源主控芯片解决方案。

6月13日,翌创微电子在上海虹桥绿地铂瑞酒店成功举办了“‘翌’路领航,创‘芯’能源”ET6000系列MCU/DSP产品发布会。在此次发布会上,翌创微电子荣耀发布了首款全国产双核Cortex-M7能源主控MCU/DSP——ET6000系列芯片。

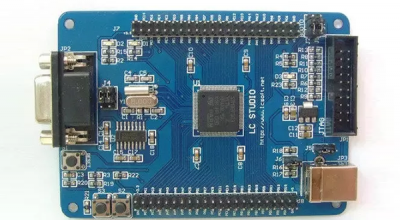

CKS32F4xx系列使用高性能的32位内核,支持浮点运算单元(FPU),同时还支持DSP指令以及存储保护(MPU)用来加强应用的安全性。

本视频将向您介绍通用开发生态系统,使您能够在一个完整的平台设计中使用低功耗PIC24F MCU和强大的dsPIC33 DSC,并演示跨器件系列的轻松移植。

首先,“嵌入式”这是个概念,准确的定义没有,各个书上都有各自的定义。但是主要思想是一样的,就是相比较PC机这种通用系统来说,嵌入式系统是个专用系统,结构精简,在硬件和软件上都只保留需要的部分,而将不需要的部分裁去。

ADI的MCU及DSP产品介绍1

演讲人:王勇

DSP处理器几乎都不具备数据的高速缓存。这是因为DSP的典型数据是数据流。也就是说,DSP处理器对每个数据样本做计算后,就丢弃,几乎不再重复使用。

DSP:

考虑一个数字信号处理的实例,比如有限冲击响应滤波器(FIR)。用数学语言来说,FIR滤波器是做一系列的点积。取一个输入量和一个序数向量,在系数和输入样本的滑动窗口间作乘法,然后将所有的乘积加起来,形成一个输出样本。

类似的运算在数字信号处理过程中大量地重复发生,使得为此设计的器件必须提供专门的支持,促成了了DSP器件与通用处理器(GPP)的分流:

步进电机已经渗透入我们生活的方方面面,本文介绍了一些重要的步进电机相关技术,为开发人员基本了解步进电机的工作原理提供了足够的信息,同时也介绍了用微控制器或数字信号处理器控制步进电机的方法。