电子工程师常犯错误大全,看看你有没有中招!

电子工程师指从事各类电子设备和信息系统研究、教学、产品设计、科技开发、生产和管理等工作的高级工程技术人才。一般分为硬件工程师和软件工程师。

硬件工程师:主要负责电路分析、设计;并以电脑软件为工具进行PCB设计,待工厂PCB制作完毕并且焊接好电子元件之后进行测试、调试。

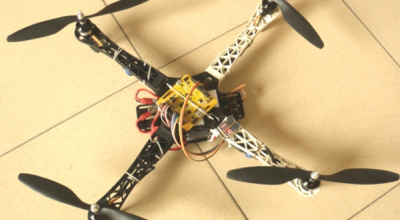

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

电子工程师指从事各类电子设备和信息系统研究、教学、产品设计、科技开发、生产和管理等工作的高级工程技术人才。一般分为硬件工程师和软件工程师。

硬件工程师:主要负责电路分析、设计;并以电脑软件为工具进行PCB设计,待工厂PCB制作完毕并且焊接好电子元件之后进行测试、调试。

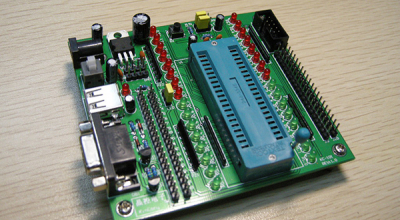

什么是单片机,相信很多人都还不知道。也不知道单片机的作用是什么。单片机简称为单片微控制器(Microcontroler),它不是完成某一个逻辑功能的芯片,而是把一个计算机系统集成到一个芯片上,相当于一个微型的计算机,因为它最早被用在工业控制领域。单片机由芯片内仅有CPU的专用处理器发展而来。

本文来源:designspark

来源:玩转单片机

单片机的40个引脚大致可分为4类:电源、时钟、控制和I/O引脚。

微控制器将在观光噪比(IoT)取向设计大多数因特网主控制元件和这些MCU将有可能被电池供电。电源效率将是实现可接受的电池寿命至关重要因此MCU将需要管理的电池使用更精确地比以往任何时候。许多MCU具有特殊的功能,帮助管理电池电量和使用这些功能优化可能使输赢在市场之间的差异。

来源:Cypress

微控制器单元(MCU)被广泛应用在电冰箱、洗衣机、空调、微波炉、吸尘器、等多种家用电器中,常用于实现电机控制、模拟传感器测量、面板控制以及在LED/LCD上显示结果等。

今天我们给大家介绍基于一款Cypress PSoC CY8C4025AZI-S413 器件的电冰箱触控面板方案,目前该方案已在品牌电冰箱中得到量产。

为了使新能源爱好者和初级研发人员更好地了解新能源汽车的核心技术,笔者结合研发过程中的经验总结,从新能源汽车分类、模块规划、电控技术和充电设施等方面进行了分析。

1新能源汽车分类

在新能源汽车分类中,“弱混、强混”与“串联、并联”不同分类方法令非业内人士感到困惑,其实这些名称是从不同角度给出的解释、并不矛盾。

建筑能耗即建筑的运行能耗,就是人们日常用能,如采暖、空调、照明、炊事、洗衣等的能耗,是建筑能耗中的主导部分。随着城市化进程的加快和人民生活质量的改善,我国建筑能耗的总量逐年上升,建筑节能状况落后,浪费及其严重。

来源:EET