单片机定时器/计数器基本原理

目前常用的单片机中往往都配备了定时器/计数器。在AT89S52芯片内包含有三个16位的定时器/计数器:T0、T1和T2,其核心是加1计数器。

目前常用的单片机中往往都配备了定时器/计数器。在AT89S52芯片内包含有三个16位的定时器/计数器:T0、T1和T2,其核心是加1计数器。

1、根据要求选择方式,确定方式控制字,写入TMOD寄存器,配置好工作模式......

一、作用

定时器/计数器以定时器的作用最为突出。一般来说涉及到定时器,都可以算作定时器算法。简单的如秒表等。复杂的如果系统内核的定时算法等。在学习单片机的路上,必学会定时器。

二、工作原理

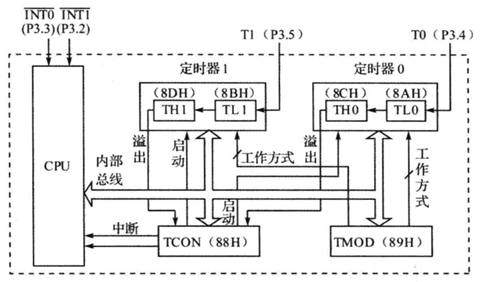

定时/计数器结构(T0和T1)

16位寄存器T0、T1分别由TH0、TL0和TH1、TL1四个8位计数器组成

方式1

当TMOD中的M0=0,M1=0时,为13位计数或定时方式,其中TLi使用低5位,其结构如图4.2所示。

在51单片机的学习过程中,我们经常会发现中断、计数器/定时器、串口是学习单片机的难点,对于初学者来说,这几部分的内容很难理解。

作者: Avi Avanindra,Devardhi Mandya,Cypress