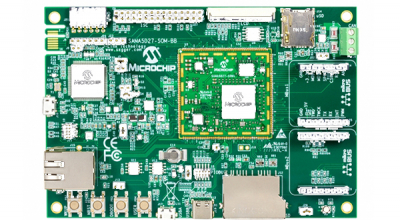

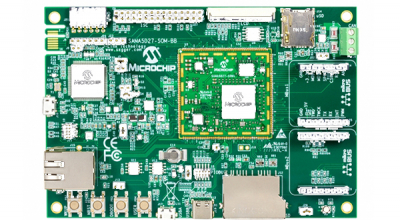

Microchip通过基于SAMA5D2 MPU的系统模块简化工业级Linux® 的设计

将电源管理、非易失性自举存储器、以太网物理层和高速DDR存储器集成在一个小型单面电路板上,让设计更紧凑、更高效

将电源管理、非易失性自举存储器、以太网物理层和高速DDR存储器集成在一个小型单面电路板上,让设计更紧凑、更高效

闪存程序存储器(Program Flash Memory,PFM)是可存储可执行代码的非易失性存储器。除指令外,它还可用于数据存储。8位PIC®单片机的PFM大小最高可扩展至128 K字,具体取决于所选器件。

前言

在面向数据的应用中,无需CPU干预即可在外设或不同存储区之间直接传输数据,从而显著改善延时和吞吐量。

存储器价格持续上涨的问题比许多人想像的更复杂...

根据市场分析师表示,动态随机存取存储器(DRAM)和NAND的价格正居高不下,而且预计还会更进一步攀升。许多人认为目前的存储器市场情况只是暂时的供需不均衡。或者,他们预期当3D NAND快闪存储器(flash)的制造趋于成熟后,就能解决目前的市场情况。然而,以DRAM的市况而言,没人能知道DRAM供应何时会改善。

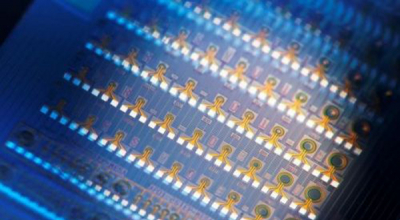

据Semi Engineering网站报导,GlobalFoundries、三星(Samsung)、台积电(TSMC)和联电(UMC)计划在2017年稍晚开始提供ST-MRAM或STT-MRAM,取代NOR Flash,此举代表市场的巨大转变,因为到目前为止,只有Everspin已经为各种应用提供MRAM,例如电池供电的SRAM替代品、读写缓存(Write Cache)等。

一、存储器格式(字对齐):

Arm体系结构将存储器看做是从零地址开始的字节的线性组合。从零字节到三字节放置第一个存储的字(32位)数据,从第四个字节到第七个字节放置第二个存储的字数据,一次排列。作为32位的微处理器,arm体系结构所支持的最大寻址空间为4GB。

存储器格式

本文介绍了一种共享高速存储器模块的设计。该高速存储器能够实现多核处理器间的数据交换,同时占用较小的电路面积。相比传统的多核处理器数据交换方式,本设计可以更好地提升系统性能。是一种有市场竞争力的电路设计结构;

1. 共享缓存结构设计

1.1 总体考虑

在本视频中,我们将介绍如何向您的器件进行边写边读操作。并简要说明各种闪存的优势。

对非边写边读闪存部分执行写入或擦除操作时,器件将处于繁忙状态...