LED大屏显示系统利用发光二极管构成的点阵模块或像素单元组成大面积显示屏显示字符、图像等信息,具有低功耗、低成本、高亮度、长寿命、宽视角等优点,近年来随着LED显示技术的不断更新,广泛应用在各类媒体场合。

LED大屏由无数个LED RGB灯组成,通过实时控制每个LED RGB的亮度及色彩,来显示不同的图案。在LED大屏显示应用中,传统的核心控制芯片选择可谓多种多样,MCU、FPGA或PLD都可以被作为核心控制芯片来进行设计,实现的效果也是各有优劣。

在LED大屏显示应用不断拓展的同时,大屏显示系统对刷新频率和延迟也提出了更严苛的要求:

更高的刷新频率:刷新频率越高,显示的图像越稳定,眼睛感觉到疲劳可能性就越小;

更低的延迟:整个数据链路的延迟进一步降低,减少闪屏或卡顿。

为确保LED大屏高刷新频率和低延迟,避免闪屏或卡顿的情况,就必须通过高速的链路来实时控制这些LED RGB灯。要实现更高刷新频率、更低延迟的LED大屏系统系统设计,主控芯片的选择非常关键。以MCU为核心的LED大屏显示控制系统常常被诟病数据处理速度无法满足实时性要求很高的场合,其实不然。

RISC-V内核的MCU,得益于RISC-V本身的简洁性和模块化设计,CPU能以更高的频率运行,带来更高的性能。因此,基于RISC-V的高主频MCU能让LED大屏显示系统实现更高的驱动频率及更高的实时性。

HPM6750就是上海先楫半导体公司开发的采用RISC-V 内核、具有高主频及创新总线架构的双核高性能MCU。HPM6750拥有两个完全独立的CPU且主频高达816MHz,模拟外设包括4组共32路精度达2.5ns的PWM、3个12位高速ADC以及1个16位高精度ADC,其性能在市场同类产品中居于领先水平。

不仅如此,对于LED大屏显示应用,高性能HPM6750能通过双千兆以太网透传的方案加双核加持完美解决高速的链路设计。HPM6750支持2个以太网控制器ENET,支持标准以太网MAC,支持10/100/1000Mbps数据传输速率,支持RMII和RGMII模式的PHY,ENET以太网控制器自带DMA,因此在数据接收和发送上CPU负载为0。HPM6750通过以太网控制器,将两个PHY收到的以太网数据相互透传,透传速率达780Mb/s。基于高性能HPM6750的LED大屏显示方案在对实时控制要求极高的应用中丝毫不逊色于FPGA方案,不仅成本更低而且进一步降低了开发难度。

< 解决方案分享>

先楫高性能MCU

LED大屏显示双千兆以太网透传应用

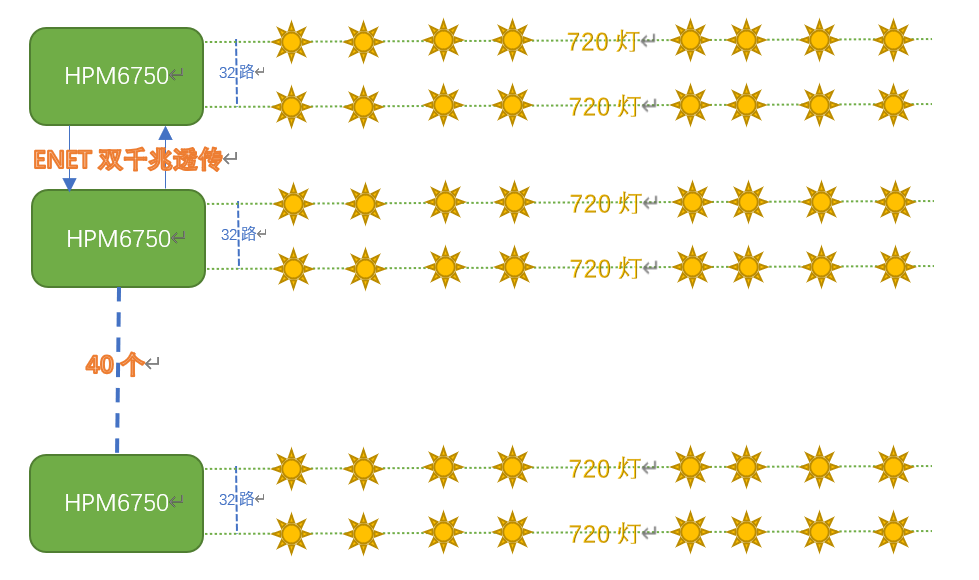

案例为720P 1280x720分辨率的LED大屏显示控制,也就是至少需要实时控制1280x720个LED RGB灯,调整亮度及色彩来显示不同的图案。为确保LED大屏高刷新率及低延迟,避免闪屏或卡顿的情况,就必须通过高速的链路来实时控制这1280x720个LED RGB灯。本案例使用两个RTL8211 RGMII模式的千兆PHY。

通信框图如下:

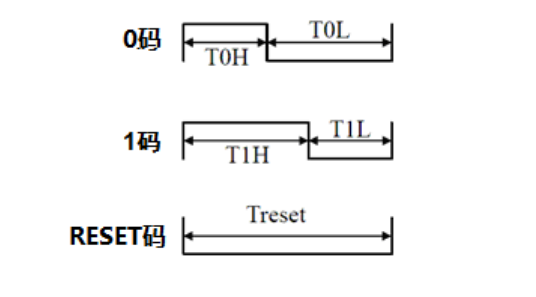

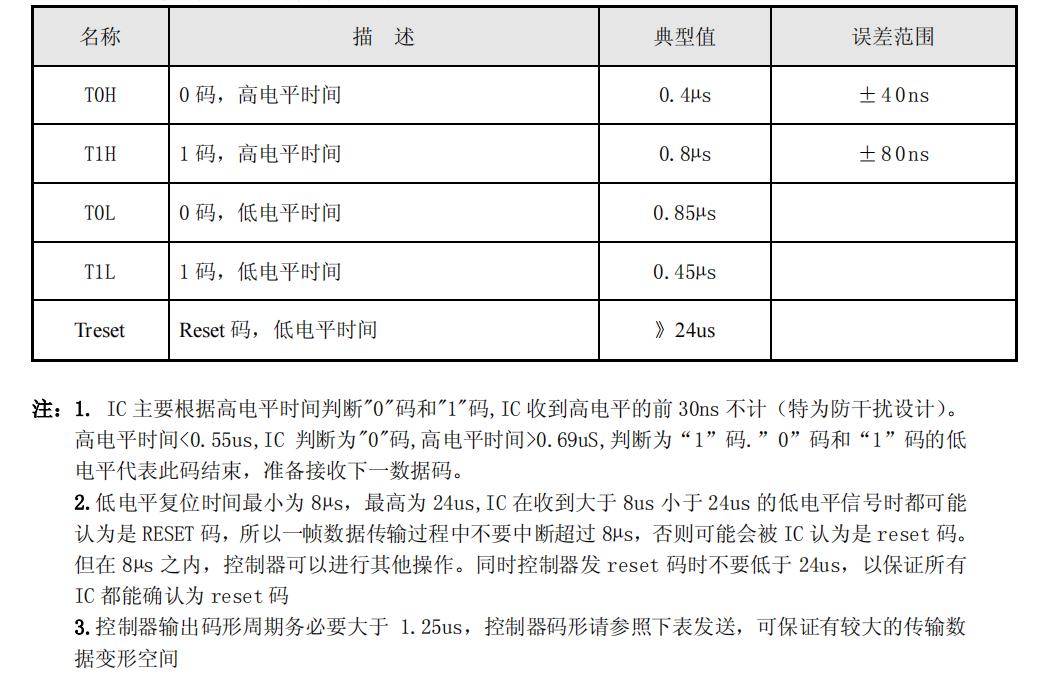

LED RGB灯需要通过特定的波形驱动,案例由UCS1903 LED驱动控制器驱动。UCS1903时序波形图如下:

整体的应用方案使用高精定时器GPTMR+DMA+GPIO的方案来驱动LED。

DMA:

HPM6750支持2个DMA控制器:XDMA和HDMA,可以实现实时的外设寄存器和内存及内存之间的数据搬移。

支持DMA请求路由器(DMAMUX)。将来自各个外设模块的DMA请求分配到16个输出信号,作为XDMA和HDMA的DMA传输请求源。

DMAMUX 的输出0-7连接到外设总线DMA控制器HDMA,DMAMUX的输出8-15连接到系统总线DMA控制器XDMA。

用户可以通过配置DMAMUX寄存器,把来自特定外设的DMA请求,连接到XDMA或者HDMA的各个通道。

DMA控制器支持8对请求-响应的握手信号,请求信号来自功能模块并经由DMAMUX路由至DMA控制器,DMA控制器根据配置使用某个通道执行改请求,完成长度为SrcBurstSize的数据传输后发送响应信号给DMAMUX,完成硬件握手。

GPTMR:

HPM6750支持11个通用定时器,每个通用定时器支持4个通道,每个通道支持32位计数器,重载寄存器和一个输入捕获/输出比较通道,支持通用计时,输入捕获,输出比较,PWM 生成,以及产生中断和DMA请求。

其中:

8 个定时器位于系统电源域称为通用定时器 GPTMR0∼7

2 个定时器位于系统电源域的 CONN 子系统,称为网络定时器 NTMR0, NTMR1

1 个定时器位于电源管理域,称为电源管理域定时器 PTMR。

GPIO:

HPM6750支持2个GPIO控制器和

2个快速GPIO控制器。快速GPIO控制器IO翻转速率可达到主频的一半400Mhz。GPIO控制器IO翻转速率在10Mhz左右。

快速GPIO控制器FGPIO是CPU私有,外设无法直接访问。

本案例中波形频率是800khz,使用GPIO控制器速率完全足够。

< 应用细节 >

为获得高刷新帧率,结合HPM6750双核加持,一个核专门用来触发ENET DMA 做网络数据透传,另一个核用来解析、转换、触发HDMA,HDMA结合GPTMR拉取波形。故网络透传、数据转换处理、拉取波形三者并发执行。

案例中使用HDMA和GPTMR硬件握手来驱动GPIO高低生成指定的波形,CPU完全不参与,CPU的工作仅仅是解析网络数据包和触发DMA,故CPU在波形产生上,负载为0。因为使用了HDMA访问,因此要强调的是HDMA访问地址必须连续,需要使用的PIN管脚必须是同一组管脚,如:PA0~31/PB0~31/PC0~31/PD0~31等。

LED控制器UCS1903波形周期为800Khz,即一个周期1250ns。一个周期分为5段,即GPTMR定时器的频率为4x800Khz=4Mhz,每段1250/5=250ns(频率及分段情况,根据实际项目调整)。1码前4高后1低(高电平时长:250x4=1000ns);0码前2高后2低(高电平时长:250x2=500ns)。每路灯驱动点亮延时(每路第一个灯珠)在4ns左右,且完全的并发。

本方案最大支持32路,以32路计算占用RAM,4(32路32bit,4byte)×5(每个周期分为5段)×24(每个灯占用24个周期)×720(每路720个灯) 为338k,。为提升执行速率,源数据建议放到DLM或SRAM中,SDRAM速率相对较慢,SRAM读写时间短,静态功耗更低,总线利用率高,更适合性能要求较高的应用。

LED大屏幕刷新频率(帧率)则和LED大屏分辨率以及LED灯组合方式相关。本案例为1280x720的分辨率,每路串联720个灯驱动需耗时21.6ms(该耗时为UCS1903物理特性,和MCU性能无关),需要1280/32=40个MCU通过千兆串联。

一帧图像的数据大小为1280x720x3(RGB三种颜色值)=2700KByte=21.1Mbit,HPM6750千兆透传速率780Mb/s, 所以一帧图片传输耗时27.05ms。

每帧数据解析后将32(每个32路)x720x3图像数据转换成指定格式并触发HDMA,实测耗时26.03ms。以上拉波形耗时21.6ms、网络传输耗时27.05ms、数据转换处理耗时26.03ms均为并行执行,故1280x720分辨率的刷新一帧耗时为27.05ms,刷新帧率36.97帧/s fps。

双千兆以太网透传速率实测可达780Mb/s,通过上面计算可以看到,HPM6750双核加持下的高速链路完全能满足实时控制需求,确保了LED大屏显示的高刷新率及低延迟。

高性能驱动

HPM6750芯片介绍

HPM6750采用双RISC-V内核,主频达816MHz,凭借先楫半导体的创新总线架构、高效的L1缓存和本地存储器,创下了高达9220CoreMark和高达4651 DMIPS 的MCU性能新纪录。与ARM Cortex-M家族中性能领先的M7相比,HPM6750的 Coremark/MHz 跑分高出约10%。

除了高算力RISC-V CPU,HPM6700系列产品还创造性地整合了一系列高性能外设,包括支持2D图形加速的显示系统、高速USB、千兆以太网、CAN FD等通讯接口,高速12位和高精度16位模数转换器,面向高性能电机控制和数字电源的运动控制系统。

来源:先楫半导体HPMicro

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。