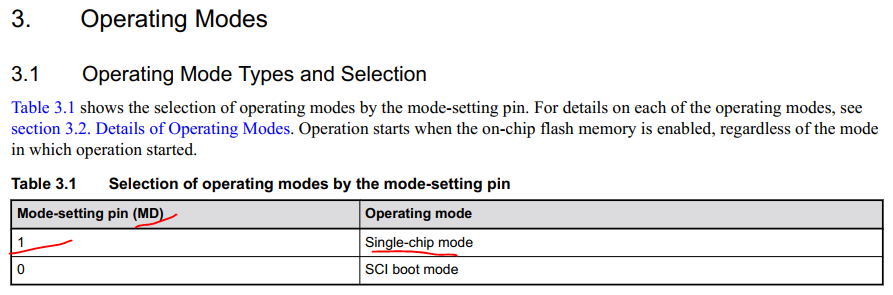

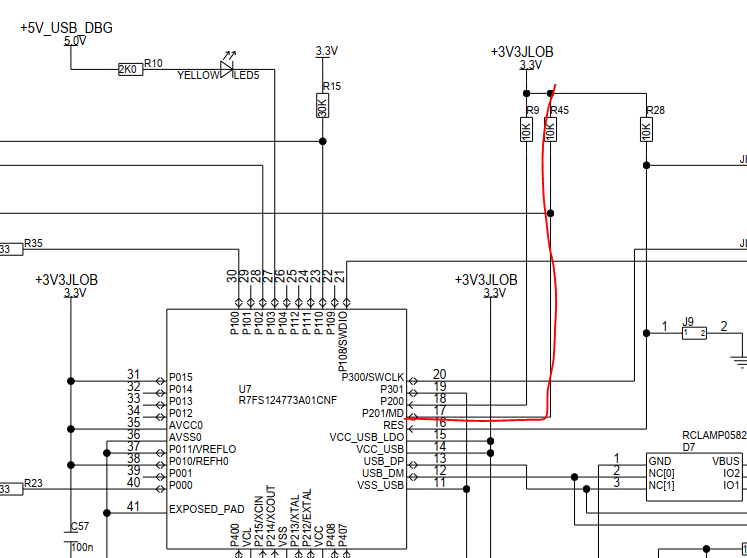

1、MD引脚上拉,MCU进入工作模式

Renesas RA2L1 Group User’s Manual: Hardware:

https://www2.renesas.cn/cn/zh/document/mah/ra2l1-group-users-manual-hardware

也可以参考看EK电路设计

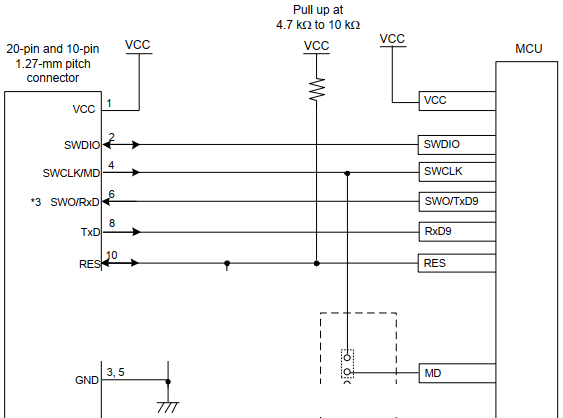

2、关于仿真和下载电路

如果要使用RFP烧写软件和FP6全功能仿真器和在线离线烧写器,必须参考以下电路进行设计。

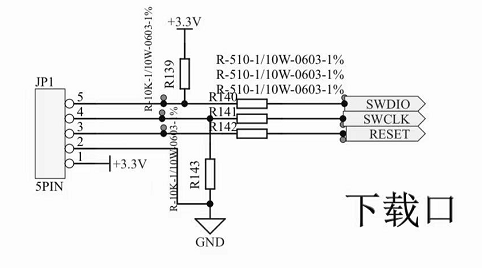

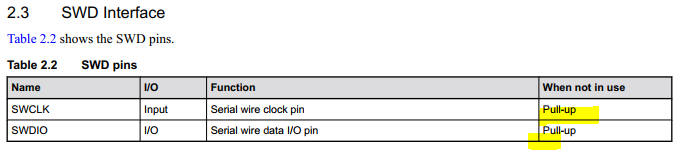

如果不需要使用RFP和FP6,可以使用以下5pin接口电路

添加MD、RXD9、TXD9,是因为RFP和FP6在下载时,必须利用RESET和MD拉低,然后通过TXD9和RXD9引脚,烧录RA2L1芯片,这里需要强调的是,只能使用RXD9和TXD9。MD引脚和SWCLK相连,不需单独引脚,省掉使用一个端口。

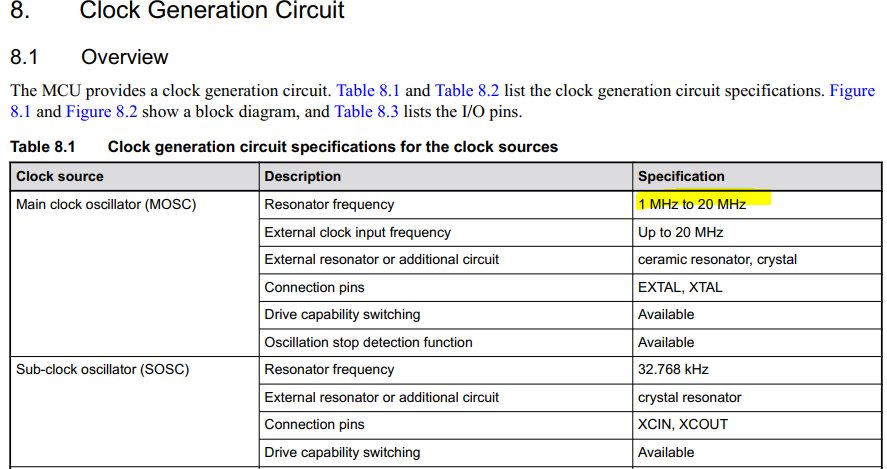

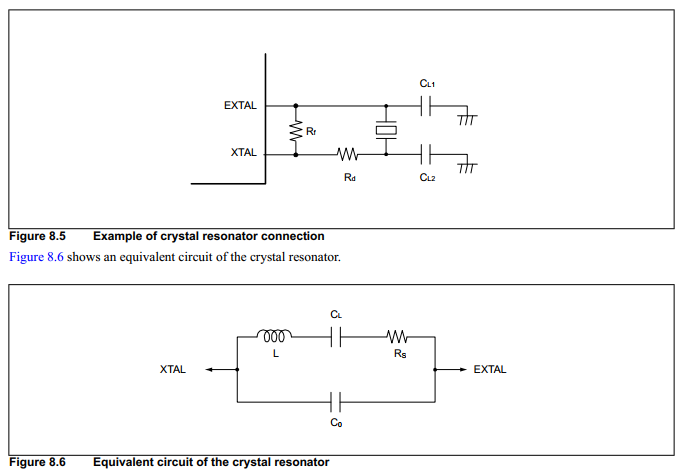

3、关于晶振电路,可以选择外部有源晶振和无源晶振,外部晶振可以选择1MHz到20MHz

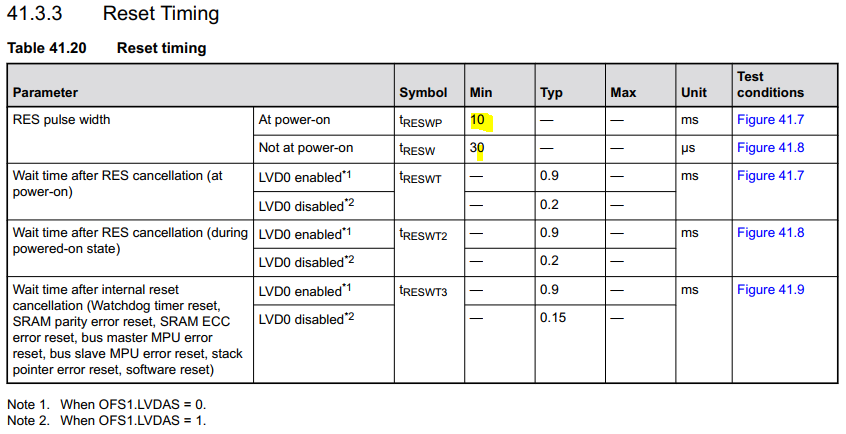

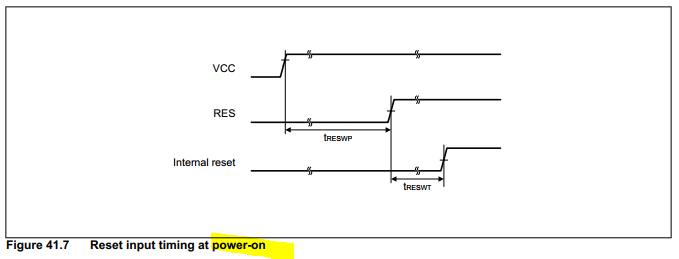

4、RESET电路,可以使用电阻和电容电路,也可以使用RESET芯片,只要保证以下时序就可以。

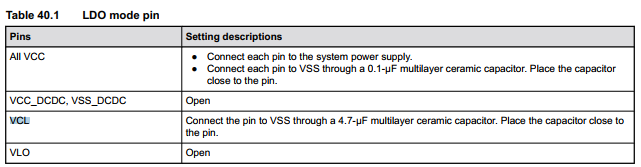

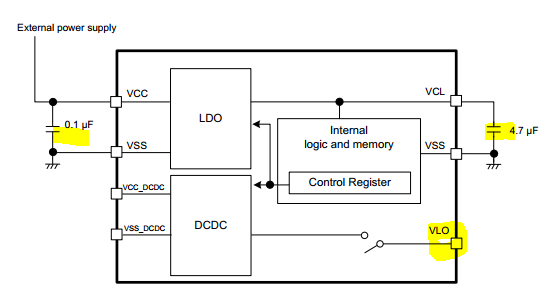

5、内部电源电路,VCL引脚必须接4.7uF电容,VLO可以输出电压。

6、未使用的引脚,根据手册推荐,一般下拉,一些功能引脚根据手册上拉。

这样的目的有两个,一个功耗最低,第二个,做干扰实验更稳定。

7、关于PCB layout问题

1)滤波电容尽量靠近MCU引脚,接地线尽量短。

2)MCU区间,不要穿越VCC线,避免以后EFT实验,受到干扰。

3)GND和AGND分开布线,一点共地,避免干扰。

来源:瑞萨MCU小百科

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。