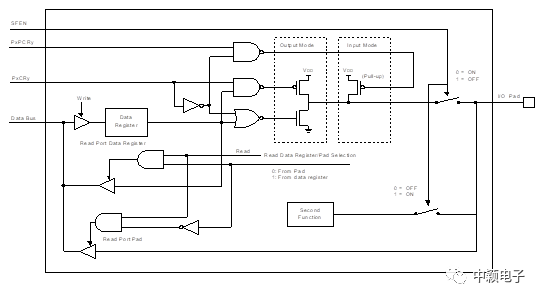

1、8bit MCU 通用I/O 结构图

端口模块如下图(79系列图):

2、相关设置寄存器及注意事项:

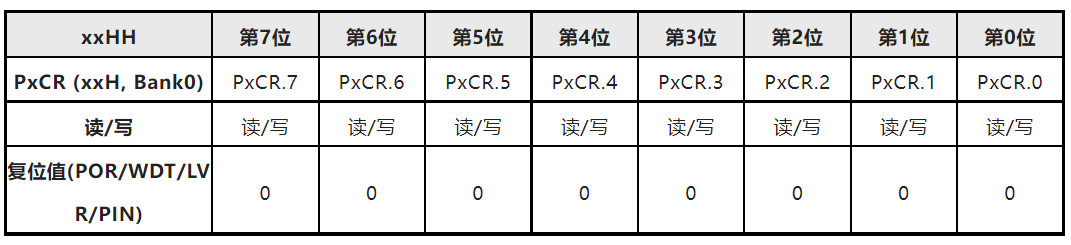

端口控制寄存器

PxCR寄存器控制I/O输入输出状态设置。

当寄存器设置成输入模式时,Px寄存器读取的是端口电平状态。

当寄存器设置成输出模式时,Px寄存器读取的是数据寄存器的值。

如有未使用到的I/O,需要设置输出固定电平以免I/O浮动电平带来的漏电流。

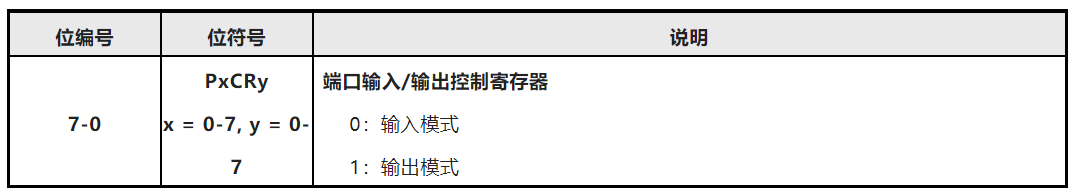

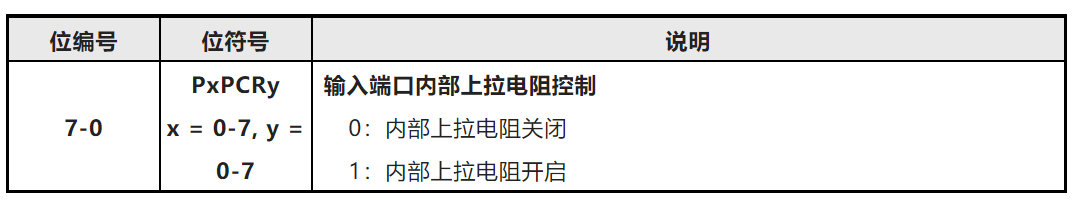

端口上拉电阻控制寄存器

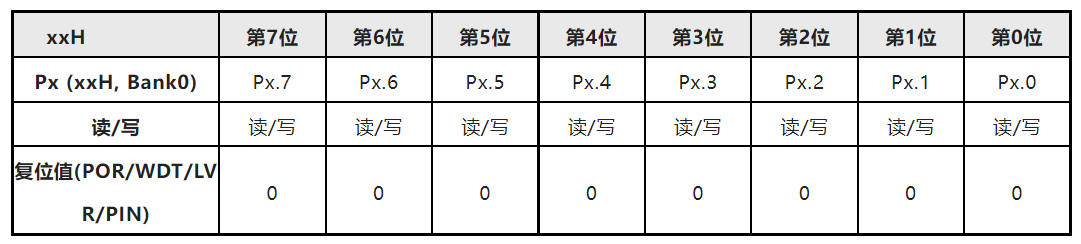

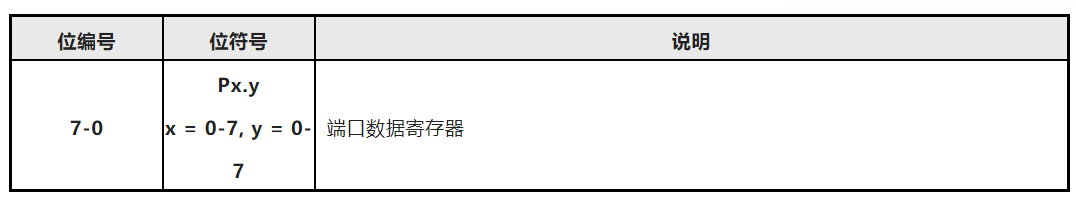

端口数据寄存器

79系列单片机 Px 寄存器都在位寻址区(例如:80H,88H等),都可以进行位寻址操作。

在初始化设施PxCR(输出状态)前,请优先设置Px寄存器,避免WDT,,OVL等复位带来的端口电平变化。

当PxCR寄存器设置成输入状态时,操作读取对应Px,是读取对应引脚电平状态。

当PxCR寄存器设置成输出状态时,根据指令来分别对应 读取的是寄存器还是引脚电平。

端口寄存器读-改-写指令举例:

ANL P0, #立即数 ; P0->立即数&(与)P0->P0

ORL P0, A ; P0->A|(或)P0->P0

INC P0 ; P0->P0+1->P0

CPL P0.0 ; P0.0->P0.0~(取反)->P0.0

引脚电平读取指令举例:

MOV A,P0 ; P0->A

MOV R0, P0 ; P0->R0

不管端口是否共享为其它功能,对端口写操作都是针对端口数据寄存器。

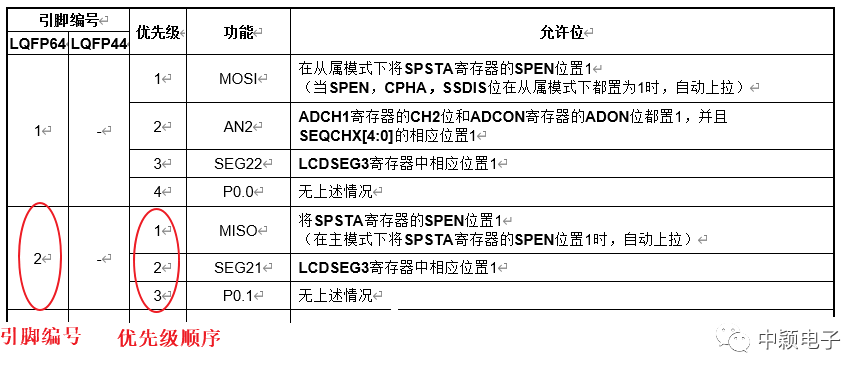

当第二功能有冲突时,按照端口共享表格中的优先级来决定输出功能。

通常I/O的优先级是低于其他功能的。

以下图为例,当P0.6引脚上BUZ功能和LED功能同时选中时,引脚输出LED波形。

当允许端口复用为其它功能时,用户可以修改PxCR﹑PxPCR,但在复用的其它功能被禁止前,这些操作不会影响端口状态。

当允许端口复用为其它功能时,任何对端口的读写操作只会影响到数据寄存器的值,端口引脚值保持不变,直到复用的其它功能关闭。

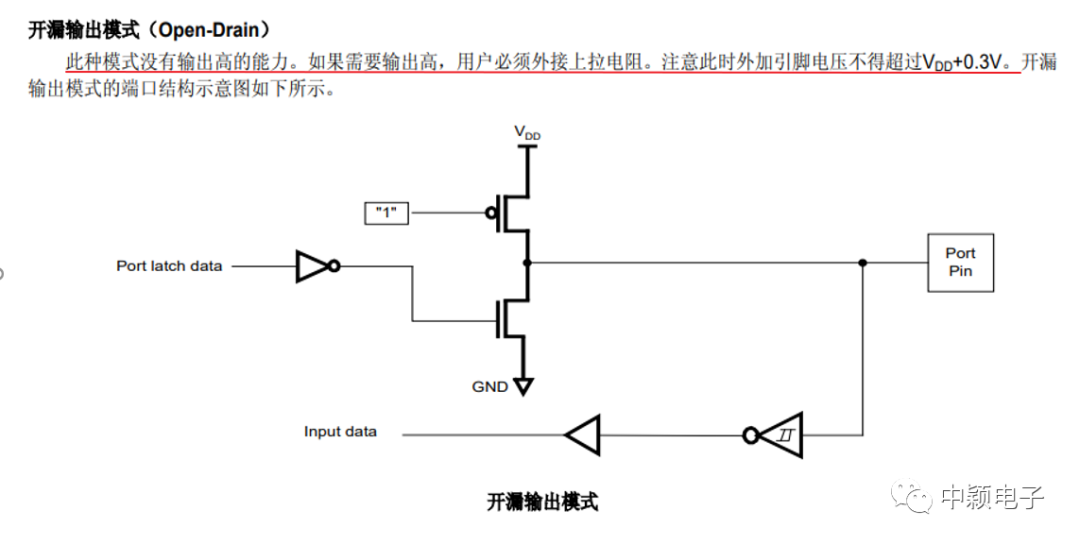

3、 I/O开漏模式介绍:

在I/O章节有选择N沟道开漏功能的寄存器时,可以实现I/O的N沟道开漏功能(注意上图红线处,IO管脚的电压不得超过VDD+0.3V电压)

如果I/O章节没有该选项的寄存器,但是又有TWI通讯功能,那么在TWI功能开启时,引脚自动切换成N沟道开沟。关闭TWI功能,自动切换回普通I/O。

芯片的电源输入端建议加去耦电路,防止VDD端出现瞬间的高压引入导致的电路损坏。

4、施密特及TTL功能介绍:

施密特功能介绍:

施密特输入特性是输入高电平阈值为0.8VDD,输入低电平阈值为0.2VDD。

VDD=5V举例,输入高电平>=4V,端口读取的电平为高,输入低电平<=1V,端口读取的电平为低。相对应的引脚是否具有施密特功能,请查询电气特性章节(输入高电压2和输入低电压2中注明有施密特功能的引脚,例如INT0-4,T3-T5等)。普通I/O不具有施密特功能。

TTL功能介绍:

TTL电平输入特性是

1) 输入高电平阈值为0.25VDD+0.8,输入低电平阈值为0.15VDD(VDD=2.7V~4.5V)

以VDD=3.3V举例,输入高电平>=1.625V,端口读取的电平为高,输入低电平<=0.495V,端口读取的电平为低。

2)输入高电平阈值为2.0V,输入低电平阈值为0.8V(VDD=4.5V~5.5V)

以VDD=5 V举例,输入高电平>=2V,端口读取的电平为高,输入低电平<=0.8V,端口读取的电平为低。

选择TTL电平功能可与VDD电压为3.3V的WIFI模块直接通过以Uart或者TWI的方式通讯,又或者直接接收外部中断信号(INT0-4),不需要外加电平转换电路。(芯片是否有TTL功能请查询I/O章节及电气特性章节)

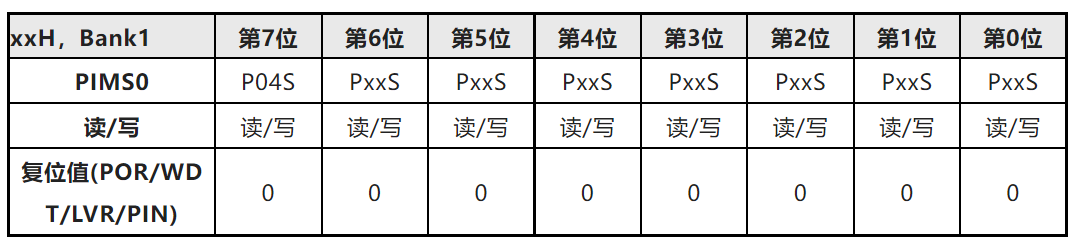

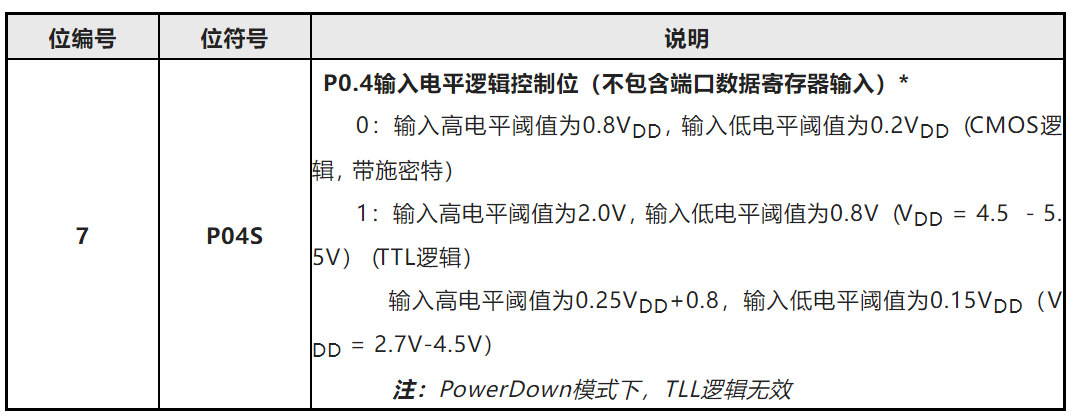

端口输入模式选择寄存器如下(TTL和CMOS选择)

*:CPU在任何情况下,读取端口数据寄存器(P0,P1……),其输入高电平阈值为0.7VDD,输入低电平阈值为0.3VDD(CMOS逻辑,无施密特);该控制位控制的是其他功能输入的逻辑电平状态,例如:INT0 - 4,RXD,SDA等数字电平输入。

注意:TTL电平特性,详情请见规格书电气特性章节。

来源:中颖电子

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。