作者:Kevin Meredith,Samtec公司产品工程师

小型化已经使得多个连接器对齐变得更加困难,而追求最优的设计实践和尽早地与连接器提供商交流有助于确保设计成功

印刷电路板(PCB板)制造商在提高可靠性和降低成本的同时,也面临着增加密度、缩小占位面积、减少侧面尺寸、管理热流和提高数据速率等重大压力。随着他们不断成功地消减这些压力,一个有趣的挑战出现在设计师们的面前,即在两片PCB板之间去对齐多个已配对连接器组。

我们所需要的是清晰明确的准则,以在不牺牲系统性能、密度和可靠性的情况下,懂得如何应对这些对齐挑战,同时满足日益严格的预算和上市时间要求。

本文在描述先进的PCB和更可靠的高密度连接器之间可能遇到的冲突性要求之前,将更详细地讨论对齐的挑战,从而可以通过使用设计最佳实践高效地满足这些要求。

小型化使连接器对齐变得困难

PCB板有许多可以改进的方向,包括密度、更高的数据速率、热管理和可靠性。然而,伴随着这些改进的是小型化这一趋势在连接器的选择和实现方面为设计师带来的压力,特别是将多个连接器配对到PCB板上。

就连接器而言,在过去25年中,小型化导致间距从0.100英寸(2.54毫米)下降到0.016英寸(0.40毫米)—— 也就是减小了六倍,因此需要更严格的公差。然而,更严格的公差本身并不是问题,问题在于标称公差周围的可变性:如果多个连接器变至标称的任一极限,则更有可能出现一些问题。

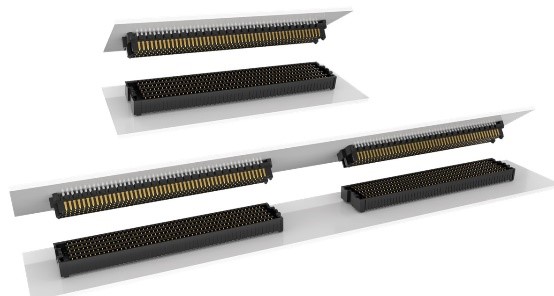

采用单个配对连接器组的应用不会出现问题:因为没有公差累加,夹层卡被假定是自由浮动的,并且连接器的整体和局部对齐功能将确保完美对齐(图1,顶部) 。

但是,在相同的母夹层卡以任何方向和任何距离增加更多配对的连接器组,都将会引入一些累加的公差(图2,底部)。这些公差对于PCB加工车间、电子制造服务以及PCB板中使用材料的属性都特别重要。

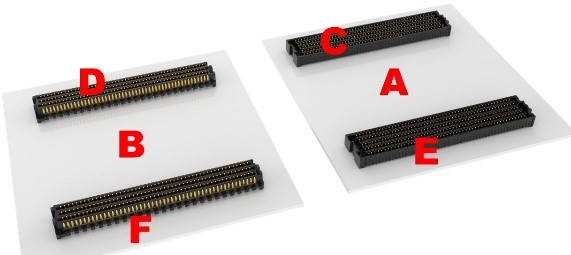

为了说明这个问题,请考虑使用一个多夹层连接器系统(图2)。该项组装包括六个或更多组件:主板(A)、夹层卡(B)、母头连接器#1(C),与配对的公头连接器#1(D),母头连接器#2(E)与公头连接器#2(F)配对。

假如夹层连接器和足够刚性的PCB板能够精确地按照标称条件被制造、加工和组装,那么可以在两个PCB板之间成功部署无限数量的连接器;事实上,公差和材料性能的可变性是限制性或决定性因素。在图2所示的情况下,设计人员需要考虑并说明所有组件的公差,包括(A)和(B)两个PCB板经常被忽略但相关的公差。

如何解决PCB板到连接器对齐的问题

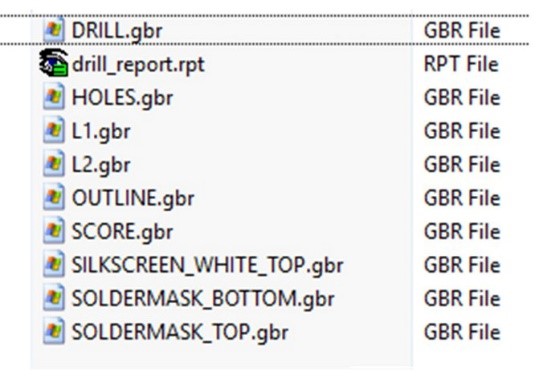

某些PCB板的采购仅受嵌入在Gerber数据包中的规格所控制(图3)。可以通过这些数据包来打造PCB板,而无需考虑机械公差。

对于多连接器应用来说,此数据包必须随附单独的机械图纸,以指示原图、钻孔和布线公差。

至此,设计师需要做两件事来帮助确保得到一个成功的结果。首先是要了解PCB板供应商和连接器供应商能提供哪些支持以确保对齐。第二是确保已进行系统级公差的研究,以确定由其设计产生的连接器对齐偏差。

回看图2中由A至F组件组成的多连接器夹层卡系统,连接器供应商只能控制连接器的公差。一家好的供应商将会达到或超过已发布的性能规格,提出PCB板公差和加工建议,甚至会根据需要为推荐的PCB供应商和设备提供参考建议。

系统或产品设计人员应参考连接器的占位尺寸和产品规格。这些文档中包含的对齐偏差规格应该与系统级公差研究的结果进行比较,以帮助确保相同板卡之间的多个连接器被成功使用。

只要不超过初始和最终的角度及线性的对齐偏差,连接器系统就能正常运行。这些对齐偏差值是通过考虑诸如绝缘体干扰、光束偏转和接触摩擦等因素来计算的。超过对齐偏差值可能会导致电路和/或绝缘体断路或损坏。

虽然设计、组件公差、设备和制造能力等所有必要的信息对于设计师通常是唾手可得,但能够与连接器制造商取得联系是很重要的,以提供更具体的指导和对对齐偏差公差累积的验证。

定位销不适用于多连接器应用

一些连接器制造商提供可选的定位销,它们通常位于连接器底部的相对侧(图4)。这些定位销有助于手动放置,可用于帮助连接器在PCB板上确定方向,且对于单连接器应用来说,它们不会增加整体公差累积。

但是,对于多连接器应用来说,我们不建议使用定位销,因为它们会对整体公差的累积产生影响。如果仍然需要在PCB板上进行定向,一个更好的选择是在PCB板上钻一些过大的孔,然后采用机器放置连接器。

同样,不建议使用卡具或销钉来辅助连接器的放置。这些方法通常依赖于PCB上相对于原图的钻孔,但是该孔的位置公差通常较差,相对另一个连接器,这就降低了最终放置的连接器的总体精度。

对于多连接器应用,更好的方法是从焊盘(solder pad)阵列A中的位置A1开始对所有焊盘进行位置校准,然后在回流之前将连接器精确放置在焊盘上。

用紧固螺钉来固定PCB板

一些特别坚固的应用可能需要使用紧固螺钉来保护两个PCB板。在这种情况下,螺钉应尽可能靠近连接器系统(图5)。

将它们放置在靠近的位置将使应力集中在连接器附近,并减小了不受支撑的PCB板跨度。跨度的增加会在PCB板中引起弯曲应力,这可能会对其他元器件,尤其是表面安装的元器件产生不利影响。

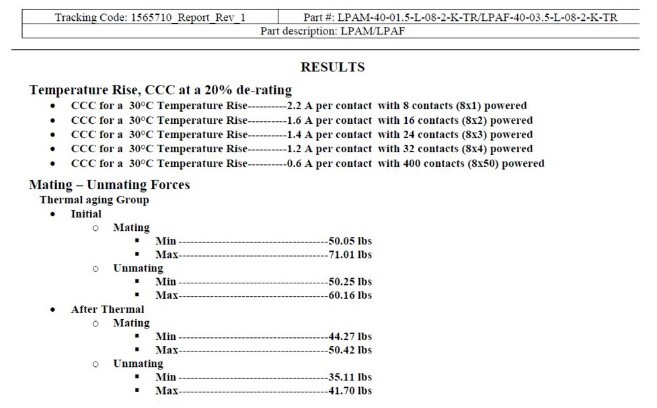

连接器衍生的PCB板应力的另一个来源是装载过程,其中大量的插入和拔出(I / O)会产生非常大的插入力/拔出力。这些力会导致PCB板过度性偏移,以致于需要额外的加强筋来支撑PCB板。非常重要的是一定要确认连接器的插入力和拔出力,它们在产品质检测试报告(图6)中可以找到。

结论

尽管小型化趋势使其更具挑战性,但通过使用最佳设计实践,还是能够在两个PCB板上使用多连接器组。这些措施包括进行系统公差研究以确定连接器对齐偏差,然后遵循连接器提供商建议的占位尺寸和模具设计,并利用机器来安放元器件。

另外,建议在设计过程的早期就与连接器提供商密切合作,因为他们可以为连接器的类型和安放提供建议,并就如何最大程度地降低PCB和连接器的整体应力提供咨询,以有助于确保设计成功。

关于作者

Kevin Meredith在连接器行业拥有27年的设计和产业经验。Kevin目前在Samtec有限公司(Samtec Inc.)担任产品工程师,此前曾在3M和Robinson Nugent就职。他是一名机械工程师,毕业于路易斯维尔大学J.B. Speed工程学院。