上一期的芝识课堂,我们带大家一起认识了东芝应用广泛的TX03系列微控制器,并且重点介绍了TX03系列中部分产品组的主要特点和应用领域。在MCU中,内核是关键单元,要应用好TX03系列MCU必须要先了解该系列所基于的Arm® Cortex®-M3内核。本期内容开始,芝子将向大家介绍Arm® Cortex®-M3内核的特点和各基本单元。

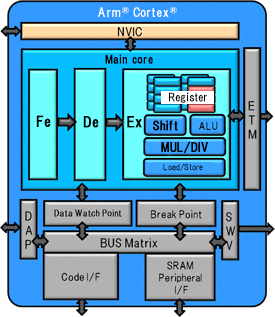

东芝的TX03系列是基于Arm® Cortex®-M3内核设计的MCU,让我们先来一起认识Arm® Cortex®-M3处理器的基本功能,方框图如图1所示。它由一个主核模块、一个控制中断的NVIC(内嵌向量中断控制器)模块、一个支持调试的功能模块和一个与外围电路进行外部连接的接口模块组成。

图1 内核结构方框图

根据图1可知,Cortex®-M3主核采用三段式流水线配置。[Fe]是读数阶段,读取PC(程序计数器)指示的存储器地址的指令;[De]作为解码阶段,对指令进行解码,并确定执行阶段的执行控制;[Ex]是执行阶段,通过Shift和ALU(算术逻辑单元)执行四则运算、逻辑运算、乘法和除法等运算,并执行加载和存储,寄存器在此阶段更新;最后[MUL/DIV]代表乘法/除法。

针对Arm处理器中断响应的问题,Cortex®-M3在内核上集成了NVIC(嵌套向量中断控制器)。NVIC模块可挂起正在主核上运行的计算处理,并控制切换到优先处理。它支持系统异常和中断的发生,如果在异常处理过程中需要有一个高优先级的异常中断,NVIC块将:

1、暂停正在处理的异常

2、启动高优先级的异常处理

3、完成高优先级的异常处理

4、恢复中断的异常处理

它可以控制嵌套,即异常中断处理。此外,它还包括调试控制功能和SysTickTimer,即操作系统(OS)进行任务管理的硬件定时器。

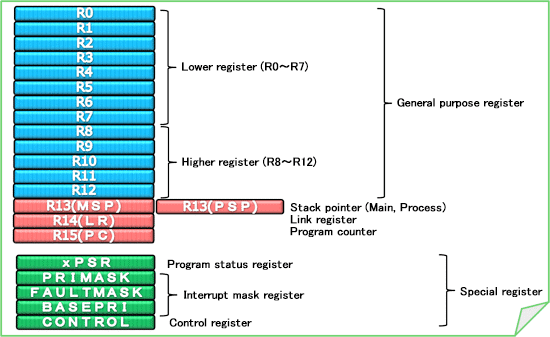

Cortex®-M3处理器具有R0至R15寄存器。R0至R12是通用寄存器。R13是可配置区域的寄存器,可以在两种堆栈指针之间切换。R14是链接寄存器,R15是程序计数器。此外,还有控制Cortex®-M3处理器特殊功能的特殊寄存器。寄存器分配如图2所示。

图2 寄存器分配示意图

图片上蓝色部分寄存器均为通用寄存器,用于输入算术单元(ALU)的数据,输出计算结果,传输存储器中储存数据的操作等。寄存器R15(PC)和R14(LR)用于控制程序执行顺序,而寄存器R13则用于堆栈指针。

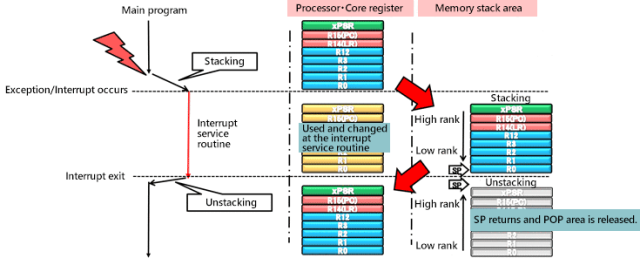

特别要注意的是,Arm® Cortex®-M3内核在异常/中断处理程序的开始和结束时会自动执行入栈和出栈功能。可自动执行入栈和出栈的寄存器有8个,分别是R0、R1、R2、R3、R12、R14、R15和xPSR。

我们来看看如图3所示的在发生异常/中断事件时,程序流程示例中的入栈和出栈操作。

图3 异常/中断事件时,程序流程的入栈和出栈操作图

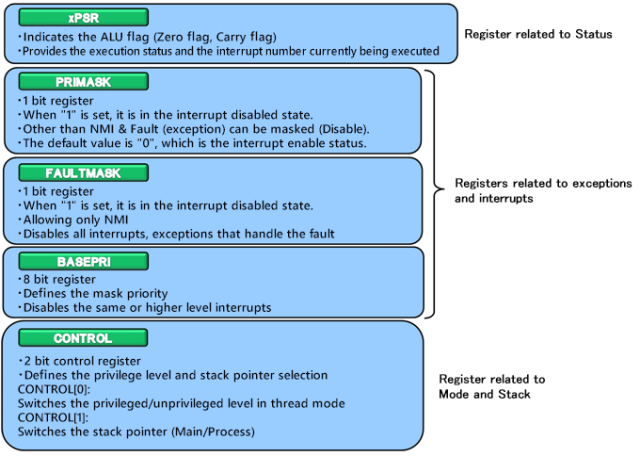

此外,Arm® Cortex®-M3还在内核水平上搭载了若干特殊功能寄存器,主要可分为三组:状态字寄存器(三合一)、中断屏蔽寄存器、控制寄存器。具体功能及描述可看图4。

图4 Arm® Cortex®-M3内核特殊寄存器功能概述

通过今天的芝识课堂,我们带大家从内核的基本结构入手,不仅学习了流水线的基本流程,还了解了该内核的寄存器相关知识和分配的规则。在随后的芝识课堂中,我们将会继续跟大家一起学习Arm® Cortex®-M3内核的操作模式和其他功能单元,请大家持续关注芝识课堂,别错过最详尽的MCU基础功能介绍哦!

来源:东芝半导体

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。