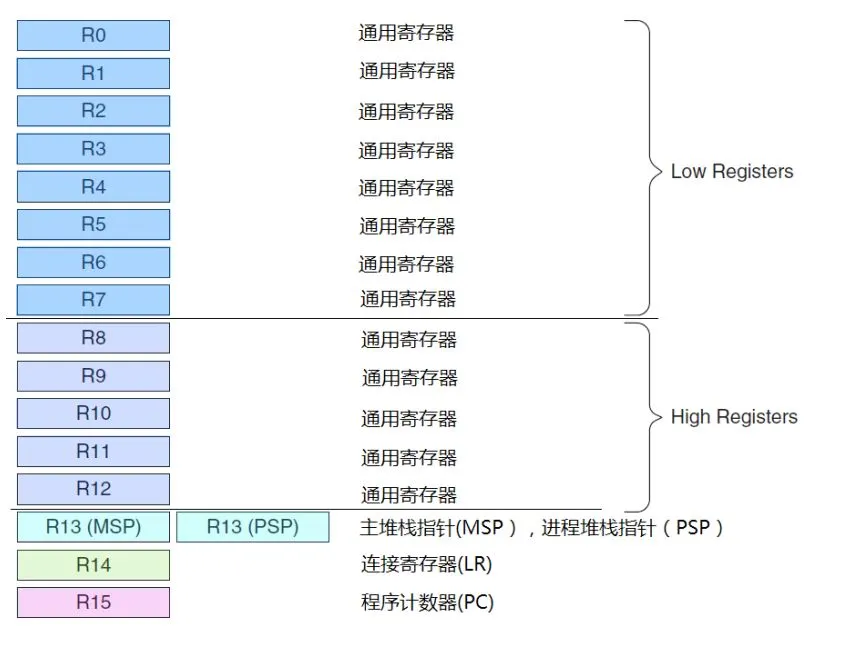

1.寄存器

Cortex-M3拥有R0~R15通用寄存器和一些特殊功能寄存器。

R0~R12这些通用寄存器,复位初始值都是不可预料的。

2.Cortex-M3有R0到R15的通用寄存器组

注:绝大部分的16位thumb只能访问R0到R7,而32位thumb-2可以访问全部寄存器

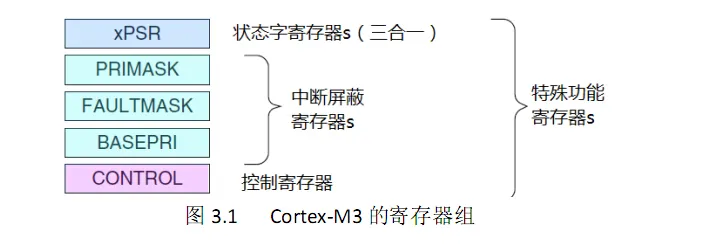

3.特殊功能寄存器

3.1程序状态寄存器组(应用程序PSR+中断号PSR+执行PSR)

3.2中断屏蔽寄存器组:用于控制异常的除能和使能

3.3控制寄存器:用于定义特权级别和当前使用哪个堆栈指针

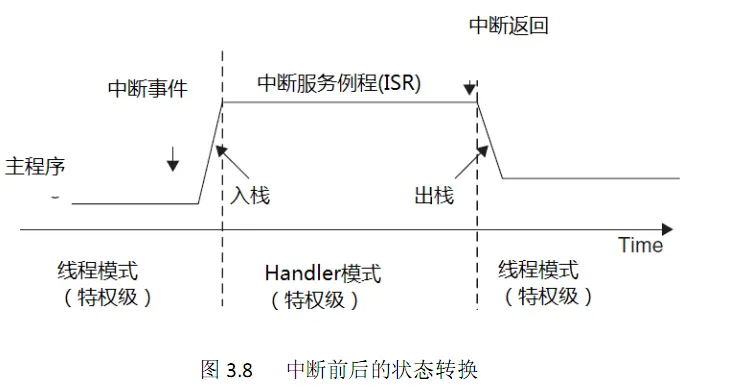

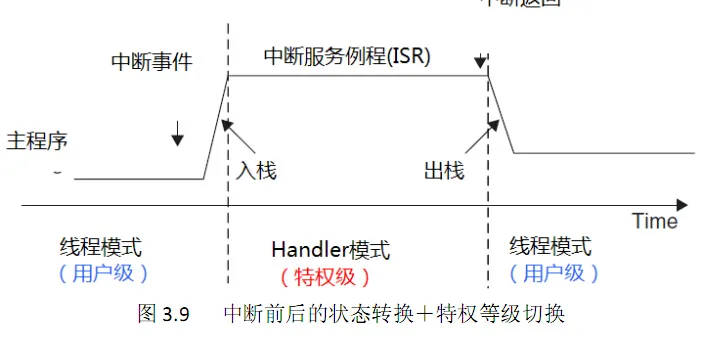

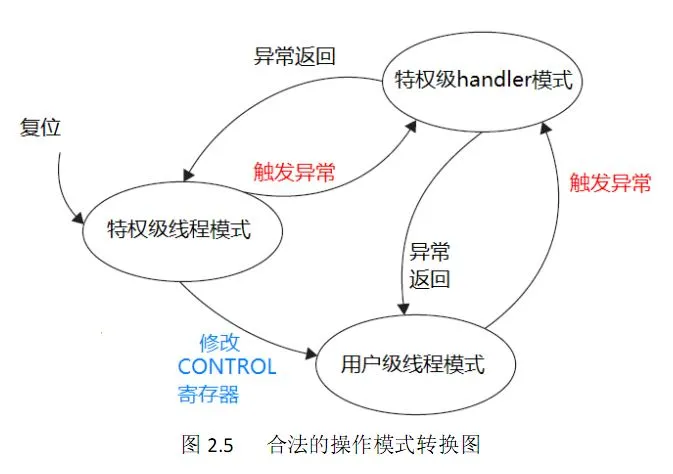

4.操作模式和特权级别:

两种操作模式(处理器模式):Handler模式和线程模式(用于区分异常服务例程的代码和普通程序的代码)

两种特权等级:特权级和用户级(是指在硬件层面上对存储器访问权限的设置)

注:Cortex-M3在运行主程序(即线程模式)可以使用特权级别和用户级别;但是异常服务例程(即handler模式)只能使用特权级别。当处于线程+用户模式时一些访问权限将被禁止

将代码区分成用户级和特权级,有利于程序架构的稳定,如某一个用户代码出问题,不会使其成为害群之狗,因为用户级别的代码是禁止对一些要害寄存器操作的。

5.异常处理

5.1CONTROL[0]=0;

5.2CONTROL[0]=1;

CONTROL[0]只有在特权级别下可以访问,若在用户级别想访问先通过"系统服务呼叫指令(SVC)"来触发SVC异常,然后在该异常的服务例程中可以修改CONTROL[0]。

6.下面是各操作模式的转换

7.异常和中断

可以有11个系统异常和最多240个外部中断(IRQ),具体芯片使用了多少要看芯片制造厂商。

作为中断功能的强化,NVIC 还有一条NMI输入信号线,具体做什么由芯片制造商决定,NMI(not masked interrupted)

8.向量表:当一个异常被Cortex-M3内核接受。对应的异常Handler就会执行,向量表用来决定Handler的入口地址。

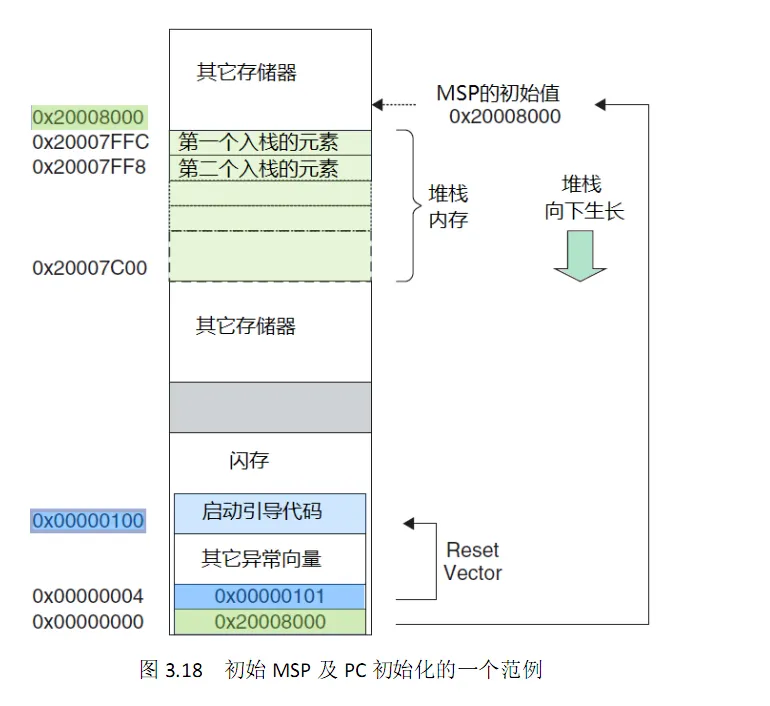

9.Cortex-M3的双堆栈:主堆栈(MSP)和进程堆栈(PSP)。是由CONTROL[1]控制的。

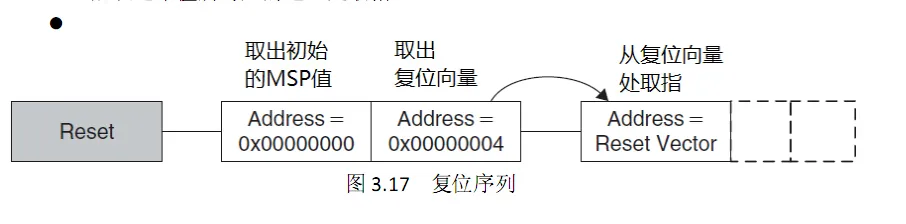

10.复位序列:

先从0X00地址取出MSP的值再从0x04地址取出PC的初始值,0X04处存的值是复位向量,而不是跳转指令。

此处Cortex-M3与ARM及单片机不同。以前ARM都是从0X00地址开始执行第一条指令,一般第一条指令都是跳转指令

11.MSP及PC初始化的一个例程

本文转载自:网络

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。