对于高速的串行总线来说,一般情况下都是通过数据编码把时钟信息嵌入到传输的数据流里,然后在接收端通过时钟恢复把时钟信息提取出来,并用这个恢复出来的时钟对数据进行采样,因此时钟恢复电路对于高速串行信号的传输和接收至关重要。

CDR电路原理

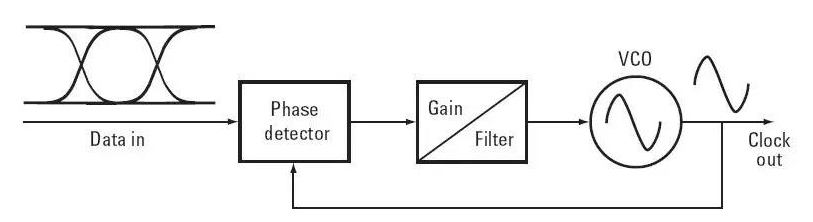

时钟恢复的目的是跟踪上发送端的时钟漂移和一部分抖动,以确保正确的数据采样。时钟恢复电路(CDR:Clock Data Recovery)一般都是通过PLL(Phase lock loop)的方式实现,如下图所示。

输入的数字信号和PLL的VCO(Voltage-controlled oscillator,压控振荡器 )进行鉴相比较,如果数据速率和VCO的输出频率间有频率差就会产生相位差的变化,鉴相器对这个相位误差进行比较并转换成相应的电压控制信号,电压控制信号经过滤波器滤波后产生对VCO的控制信号从而调整VCO的输出时钟频率。

使用滤波器的目的是把快速的相位变化信息积分后转换成相对缓慢的电压变化以调整VCO的输出频率,这个滤波器有时又称为环路滤波器,通常是一个低通的滤波器。通过反复的鉴相和调整,最终VCO的输出信号频率和输入的数字信号的变化频率一致,这时PLL电路就进入锁定状态。

环路带宽对眼图、抖动测量的影响

值得注意的是,在真实的情况下,输入的数字信号并不是一个纯净的信号,而是包含了不同频率成分的抖动。对于低频的抖动来说,其造成的是数据速率的缓慢变化,如果这个缓慢变化的频率低于环路滤波器的带宽,输入信号抖动造成的相位变化信息就可以通过环路滤波器从而产生对VCO输出频率的调整,这时VCO的输出时钟中就会跟踪上输入信号的抖动。

而如果输入信号中抖动的频率比较高,其造成的相位变化信号不能通过环路滤波器,则VCO输出的时钟中就不会有随输入信号一起变化的抖动成分,也就是说输入信号中的高频抖动成分被PLL电路过滤掉了。

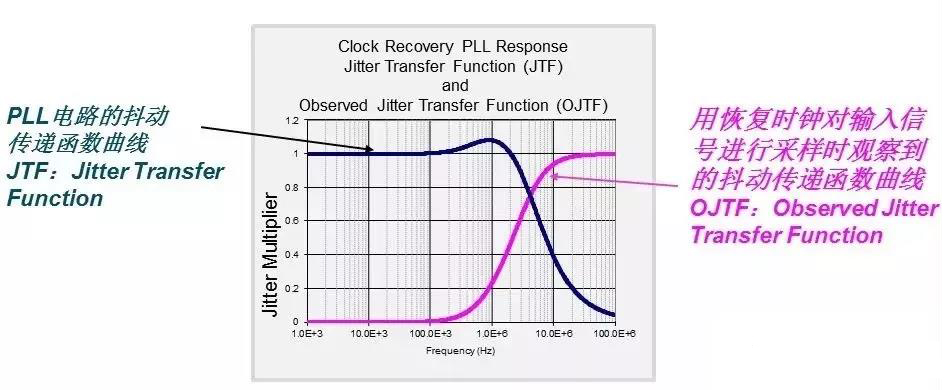

如下图所示,我们通常会用PLL电路的JTF(Jitter Transfer Function,抖动传递函数)曲线描述PLL电路对于不同频率抖动的传递能力。JTF曲线通常是个低通的特性,反映了PLL电路对于低频抖动能很好跟踪而对高频抖动跟踪能力有限的特性。

对于低频的抖动,PLL电路能够很好地跟踪,恢复出来的时钟和被测信号一起抖动。如果接收端的芯片用这个恢复时钟为基准对输入信号进行采样,由于此时时钟和被测信号一起抖动,所以这种低频的抖动不会被观察到,对于数据采样的建立保持时间也没有太大影响。

相反地,高频的抖动会被PLL电路过滤掉,因此输出的时钟里不包含这些高频的抖动成分。如果用这个时钟对数据信号进行采样,就会观察到输入信号里明显的抖动。接收端用恢复时钟进行采样时能够看到的抖动与抖动频率间的关系有时我们会用OJTF(Observed Jitter Transfer Function,观察到的抖动传递函数)曲线来描述,其随频率的变化曲线正好JTF曲线相反。

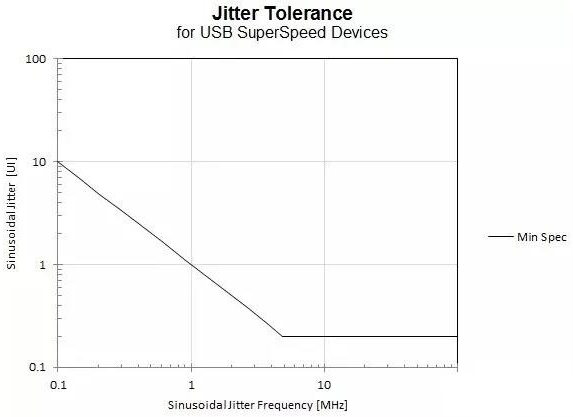

正因为时钟恢复电路对于低频抖动的跟踪特性,因此很多高速串行总线的接收芯片对于低频抖动的容忍能力会远远超过对高频抖动的容忍能力。下图是USB3.0总线对于接收端芯片对于不同频率抖动容忍能力的要求的一条曲线,可以看到其对低频的容忍能力非常大,甚至可以远超过1个UI(数据比特宽度)。

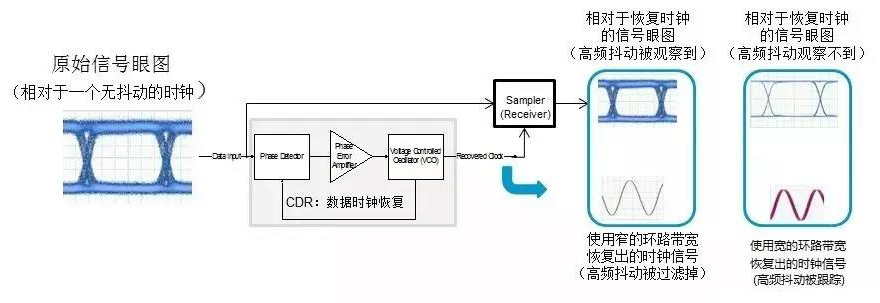

时钟恢复电路的PLL的环路带宽设置不同,对于不同频率抖动跟踪能力也不一样。一般情况下,PLL的带宽设置越窄,恢复出来的时钟越纯净,但是对于抖动的跟踪能力越弱,用这个时钟为基准对数据做采样时看到的信号上的抖动会越多,看到的信号的眼图会越恶劣。

相反,如果PLL的带宽设置越宽,对于抖动的跟踪能力越强,恢复出来的时钟和信号的抖动越接近,用这个时钟为基准对数据做采样时看到的信号上的抖动会越少,看到的信号的眼图会越好。下图反映出的就是不同的PLL带宽设置对于恢复时钟抖动和以这个恢复时钟为基准对信号进行采样时看到的眼图的情况。

转自:至秦单片机