RTC为整个电子系统提供时间基准,主控设计均离不开RTC电路设计,在应用RTC时,会出现精度或功耗大的现象,如何解决RTC精度及功耗问题?本文将为您介绍时钟芯片应用问题及解决方法。

一、什么是RTC

实时时钟(Real_Time Clock)简称为RTC,主要为各种电子系统提供时间基准。通常把集成于芯片内部的RTC称为片内RTC,在芯片外扩展的RTC称为外部RTC,PCF8563是一款低功耗的CMOS实时时钟/日历外部芯片,支持可编程时钟输出、中断输出、低压检测等,与处理器通过I2C串行总线进行通信,最大总线速率可达400kHz。

二、RTC精度设计

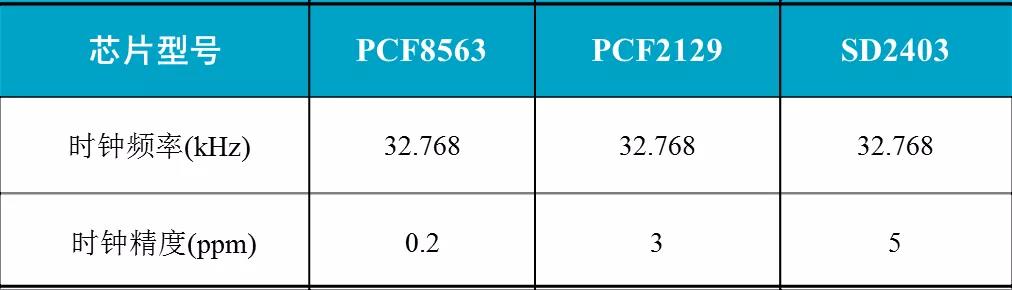

RTC的主要职责就是提供准确的时间基准,计时不准的RTC毫无价值可言。目前部分MCU在片内已集成RTC,实际测试中在电池供电6小时环境下片内RTC的偏差在1-2分钟。因此,若对实时时钟有较高的要求则需优先考虑外扩RTC,同时要求时钟精度更高的RTC,比如PCF8563,表1所示是不同RTC的时钟精度对比。

1、电路设计

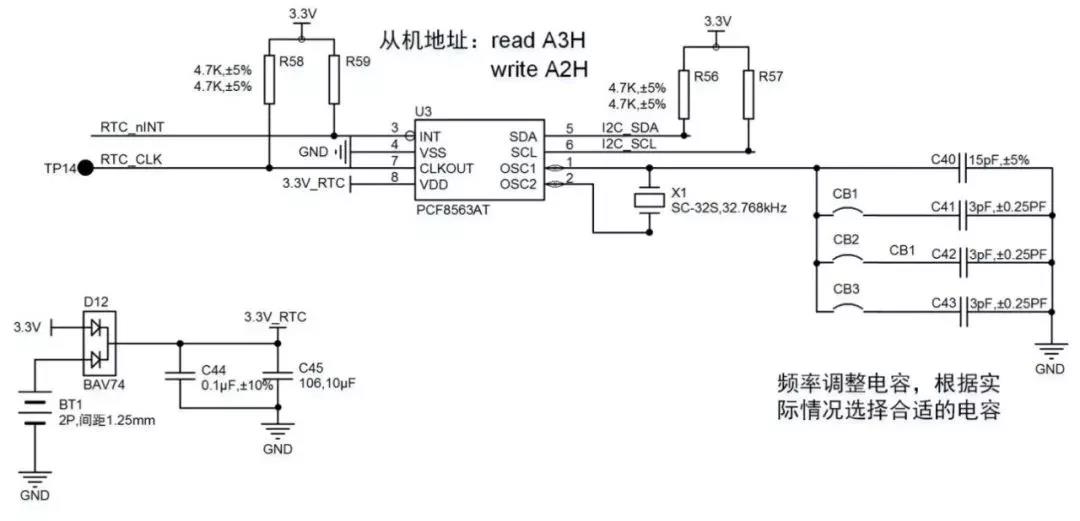

RTC设计电路简约而不简单,时钟芯片的选择、晶振的选择、电路设计、器件放置、阻抗控制、PCB走线规范均会影响RTC的时间基准的稳定性,图1为RTC芯片PCF8563电路设计。

2、晶体对地电容容值选择

负载电容:

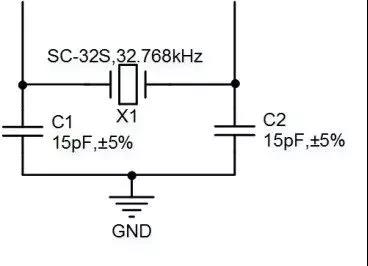

Cload= [ (Ca*Cb)/(Ca+Cb) ]+Cstray

其中Ca、Cb为接在晶体两引脚到地的电容,Cstray为晶体引脚至处理器晶体管脚的走线电容(即杂散电容总和),一般Cstray的典型值取4~6pF之间;

如要满足晶体12.5pF负载电容的要求:

Cload= [ (15*15)/(15+15) ]+5=12.5pF

3、PCB布线

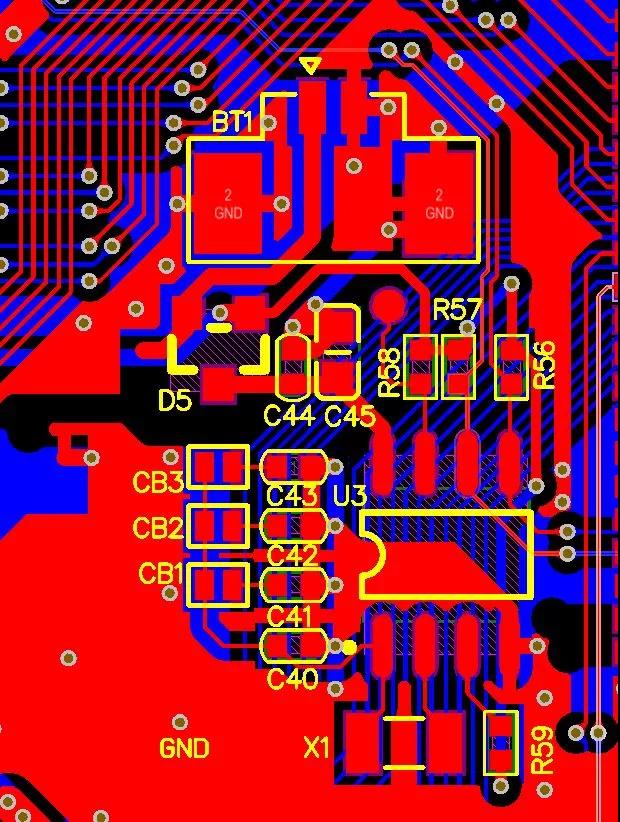

由于RTC的晶振输入电路具有很高的输入阻抗,因此它与晶振的连线犹如一个天线,很容易耦合系统其余电路的高频干扰。而干扰信号被耦合到晶振引脚导致时钟数的增加或者减少,考虑到线路板上大多数信号的频率高于32.768kHz,所以通常会发生额外的时钟脉冲计数,因此晶振应尽可能靠近OSC1和OSC2引脚放置,同时晶振、OSC1和OSC2的引脚最好布成地平面,具体PCB布线如图3所示。

4、电路相关说明

如图1所示,R56、R57为I2C总线上拉电阻,PCF8563中断输出及时钟输出均为开漏输出,所以也需要外接上拉电阻,如图1中的的R58、R59,若不使用这两个信号,对应的上拉电阻可以不用。

对于PCF8563芯片,需外接时钟晶振32.768kHz(如图1的X1),推荐使用±20ppm或更稳定的晶振。PCF8563典型应用电路推荐使用15pF的晶振匹配电容,实际应用时可以作相应的调整,以使RTC获得更高精度的时钟源。一般晶振匹配电容在15pF~21pF之间调整(相对于±20ppm精度的32.768kHz晶振),15pF电容时时钟频率略偏高,21pF电容时时钟频率略偏低。

5、精度调整方法

- 设置PCF8563时钟输出有效(CLKOUT),输出频率为32.768kHz;

- 使用高精度频率计测量CLKOUT输出的频率;

- 根据测出的频率,对CB1、CB2、CB3作短接或断开调整,频率比32.768kHz偏高时,加大电容值,频率比32.768kHz偏低时,减小电容值。

说明:图1中的C41、C42、C43的值在1pF~3pF之间,根据实际情况确定组合方式,以便于快速调整,推荐使用(3pF、3pF、3pF)、(1pF、2pF、3pF)、(2pF、3pF、4pF)。

三、RTC低功耗设计

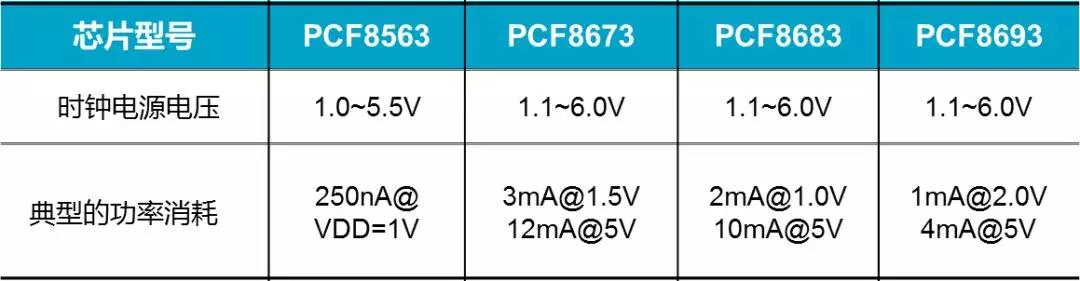

很多RTC设计成可以只依靠一块电池供电就能工作,如果主电源关闭,仅依靠一小块锂电池就能够驱动振荡器和整个时钟电路,如何降低RTC电路工作时功率消耗?

通过应用几种不同的方法可以降低RTC功耗:

本文转自: ZLG立功科技,转载此文目的在于传递更多信息,版权归原作者所有。