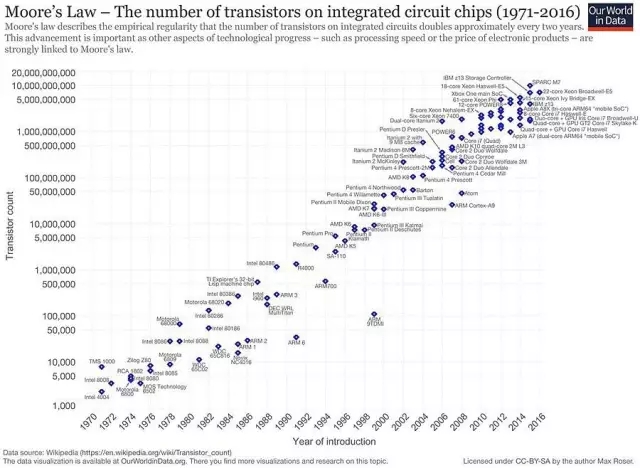

本月早些时候公布的“2015年半导体国际技术路线图”(ITRS)显示,经过50多年的微型化,晶体管的尺寸可能将在五年后停止缩减。

该报告预测,在2021年后,继续缩小微处理器中晶体管的尺寸,对公司而言在经济上不可取。相反,芯片制造商将用其他方法增大晶体管密度,即将晶体管从水平结构,转变为垂直结构并建造多层电路。

一些人认为,这一变化相当于是宣布摩尔定律的终结。雪上加霜的是,这是最后一份ITRS路线图。

ITRS由美国发起,而后扩展到全球,已有20年的历史,现在却走到了终点。

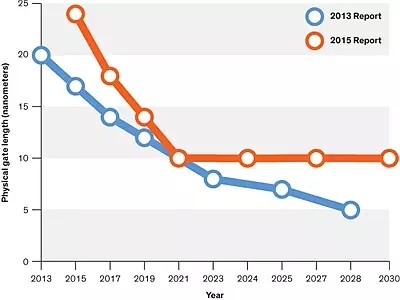

1971年到2016年,全球半导体行业根据摩尔定律,在电路板上容纳的晶体管数量

半导体特性不再由半导体公司决定

因为行业参与度的减少以及打算着手其他项目,美国半导体行业协会(SIA)——美国的一个贸易集团,代表IBM、英特尔以及华盛顿其他公司的利益,是ITRS的主办方之一——将离开ITRS,与半导体研究公司(SRC)合作,参与政府和行业支持的重点研究项目。

ITRS的其他参与者将以新的名义继续制定路线图 ITRS 2.0,并将其作为IEEE计划“Rebooting Computing”的一部分。

ITRS的转变似乎只是微小的行政变动。但是,VLSL公司的分析员Dan Hutcheson表示,这是行业的大地震。20世纪90年代早期,为了制定路线图,美国的半导体公司进行合作、确定共同需求,最终于1998年成立了ITRS。Hutcheson说,供应商很难知道半导体公司需要什么,因此,芯片公司就要集体制定优先次序以便充分利用有限的研发资金。

然而,按照摩尔定律的规律发展,给各个公司带来困难和大的开支,导致行业内出现重大整合。据Hutcheson统计,2001年有19家公司开发、制造装有先进晶体管的逻辑芯片。而今天,只有4家公司:英特尔、三星、台积电和GlobalFoundries(此前,IBM也属于这一行列,只是近期将其芯片制造厂卖给了GlobalFoundries)。

Hutcheson表示,这些公司有自己的路线图,可以直接与自己的设备和材料供应商交流。此外,它们之间的竞争十分激烈。

“这个行业已经变了,”ITRS的主席Paolo Gargini说,但是他还强调了其他的转变。不再自己制造尖端芯片的半导体公司,靠的是工厂为其芯片提供先进技术。Gargini还说,芯片购买方和设计方,如苹果、谷歌和高通,越来越能决定未来芯片的要求。

“以前,是半导体公司决定半导体的特性,而现在的情况完全不同。”

ITRS 2.0:摩尔定律并没有死亡

最新的这份ITRS报告的命名是ITRS 2.0。这一名称反映了计算的改进不再是来自自下而上的推动——使用更小的交换机和密度更大、速度更快的内存。相反,现在更多的是依靠自上而下的方法,注重能促进芯片设计的各种应用,如数据中心、物联网和移动设备。

实际上,在2014年4月,ITRS 委员会便宣布,他们决定重组 “ITRS 路线图”,以适应半导体行业不断发展的需求。新的 ITRS 2.0 将聚焦 7 大主题:

系统集成:关注如何从设计上在计算机体系架构中整合异构模块

系统外连接:关注无线技术

异构集成:如何将不同技术集成为一体

异构组件:MEMS、传感器等其他系统设备

非 CMOS 结构:自旋电子学、忆阻器以及其他不是基于 CMOS 的设备

摩尔定律升级(More Moore):继续关注 CMOS 元件缩小

工场集成:关注新的半导体生产工具和工艺

这次新发布的报告,就属于“摩尔定律升级”研究组的成果。

根据最近的新闻报道,新的IEEE路线图——International Roadmap for Devices and Systems——也将使用这种方法,但是会增加计算机体系结构,允许“一个全面的、端到端的计算生态系统视图,包括设备、组件、系统、体系结构和软件”。

对比2013年报告与2015年报告可以发现,半导体体积将在2021年迎来巨变

2014年,上一份 ITRS 报告预测,晶体管微型化仍是长期趋势。该报告预测,至少在2028年前,晶体管的栅极长度——电流必须在晶体管流过的距离——以及其他重要逻辑芯片的尺寸将继续缩小。

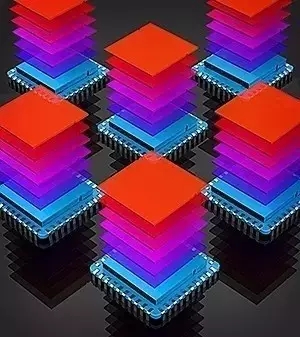

可是,自2014年以来,三维架构的概念发展越来越快。内存产业已经转向了三维架构,以减轻微型化的压力和提高NAND Flash的容量。单片三维集成——建造多层设备,层层叠加,彼此用密集的电线相连——也成为越来越受欢迎的讨论主题。

新的报告包括了这些趋势,预测了传统芯片尺寸缩小的趋势将于本世纪20年代初终结。但是,摩尔定律终结这个观点是“完全错误的”。

Gargini 说,“媒体想出了各种方式来解释摩尔定律,但是,摩尔定律只有一个定义:晶体管的数量每两年增加一倍。” 他强调:摩尔定律只是简单地预测,给定的一个集成电路区域能容纳多少晶体管,而不管是在单层的还是多层的芯片。

如果有哪一家公司愿意,它在2020年后也可以继续缩小晶体管的尺寸,只不过使用三维芯片要更划算——这就是报告想传达的信息。

换句话说,通过使用3D堆叠等新的技术,短期内芯片的晶体管密度将继续提高。这也是 ITRS 2.0 “持续关注CMOS 元件缩小”的原因。

物联网时代的到来,将产生数以百亿计的连接设备,每台设备都需要相应的芯片。而且,不同于PC和手机,很多物联网终端不需要太强的本地计算能力,半导体厂商并不需要继续突破硬件的物理极限,他们面前已经出现了新的市场和趋势——软件与硬件的结合越发紧密。

在这种新常态下,云计算、软件,以及全新的计算架构将成为未来计算技术进步的关键。

与以往首先改善硬件,软件随后跟上的趋势不同,以后半导体行业的发展将会呈现以软件为主导的软硬结合新思路:先看手机、物联网设备及数据中心等软件的需求,再回过头来决定支持这些软件和应用需要怎样的处理能力,并由此规划硬件的设计。

未来半导体发展

同时发生的还有其他的变化。

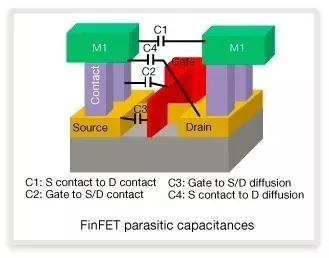

ITRS预测,几年过后,在使用三维集成之前,前沿芯片公司将放弃现在用于高性能芯片中的晶体管结构:鳍式场效应晶体管FinFET(见上图)。

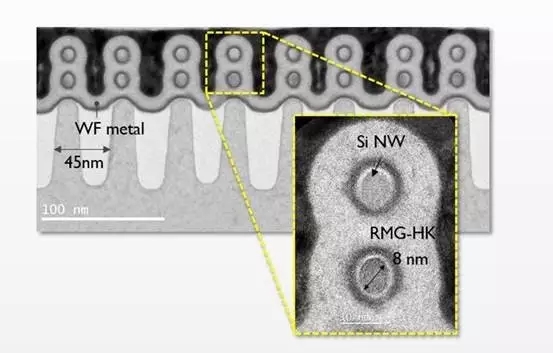

在FinFET的架构中,栅门成类似鱼鳍的叉状3D架构,可于电路的两侧控制电路的接通与断开。据这次的路线图显示,芯片制造商将会放弃FinFET,选择另一种晶体管——具有横向环绕栅极,有与FinFET类似的水平通道,但是被一个向下延伸的栅极包围(见下图)。

在那之后,晶体管将变为垂直架构,通道将采用支柱的形状,或是纳米线竖立着。

传统硅通道也将被其他材质的通道取代,即硅锗、锗、来自元素周期表第III和V列元素组成的化合物。

这些变化将使得芯片厂商能在同样大的区域装下更多的晶体管,这也就遵守了摩尔定律。

报告指出,半导体行业在短期(2015 年到2022年)和长期(2023年到2030年)所分别面临的挑战将是:

短期

硅基CMOS尺寸缩小

高迁移率沟道材料的实现

DRAM 和 SRAM尺寸缩小

高密度非易失存储尺寸缩小

材料,制程、结构变化及新的应用的可靠性

长期

先进多栅结构的实现

新存储结构的研发与实现

新器件、结构和材料的可靠性

功耗下降

多种功能的集成

但是,遵循摩尔定律的精神——计算性能稳定增长——则是另外一回事。

2015年,IEEE计算机协会主席和IEEE重启计算项目的联合领导人Tom Conte表示,晶体管密度增加一倍,有时并不等同于计算性能提高。

长期以来,晶体管尺寸缩小意味着速度更快。然而Conte说,在上世纪90年代中期,晶体管数量越来越多,但由此导致的能耗也越来越大,反而导致计算速度延迟,于是工程师重新设计的芯片的微体系结构来提高性能。十年过后,晶体管的密度已经非常大了,逼近极限。芯片厂商不得不在电路板上封装多核芯片以维持情况,这也是IEEE提出新路线图的原因。

来源:物联网智库